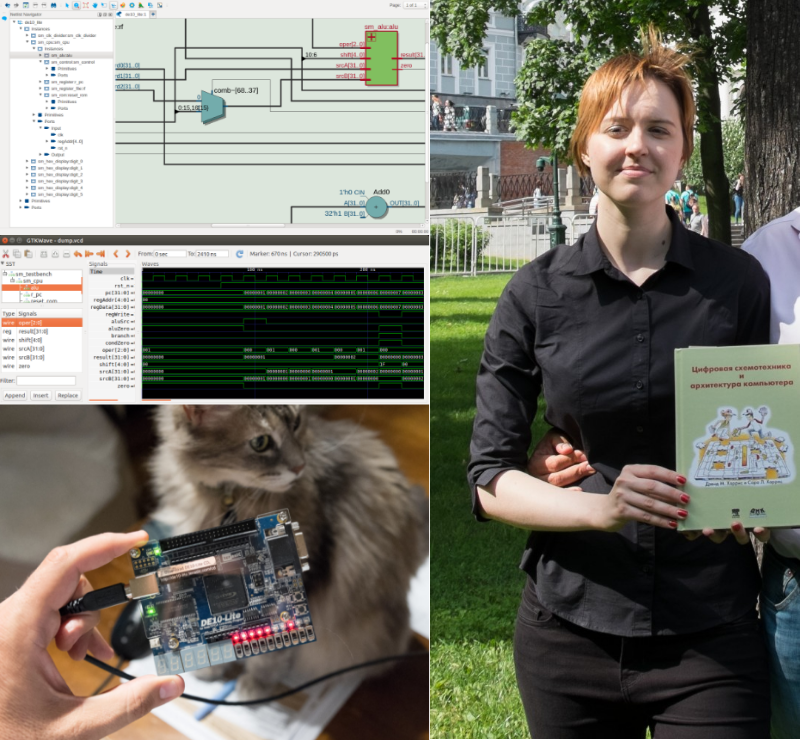

Недавно вышло еще одно печатное издание книжки Харрис & Харрис на русском языке. Это широкоохватывающий ликбез про то, как проектируют микросхемы в компаниях типа Apple и Intel (методология проектирования на уровне регистровых передач с использованием языков описания аппаратуры). До этого печатного издания вышло бесплатное электронное издание этой же книжки, которое стало вирусным — его скачивания дважды завалили британский сайт Imagination Technologies, а посты о книжке на Хабре и Гиктаймс собрали более 300,000 просмотров (1, 2, 3, 4, 5 ). История перевода книжки на русский тоже довольно поучительна — он начался как общественный проект группы энтузиастов: преподавателей российских и украинских университетов, а также русских сотрудников компаний как в Silicon Valley (MIPS, AMD, Synopsys, Apple, NVidia ...) так и в России (НИИСИ, МЦСТ, Модуль ...). Когда вышло первое печатное издание на русском языке, его тоже довольно быстро раскупили и пожаловались, что оно черно-белое. Поэтому следующий принт был цветной, улучшенного качества.

Теперь возникает вопрос: ну хорошо, вы приобрели или скачали бесплатно книжку, поняли основы цифровой схемотехники, языков описания аппаратуры Verilog и VHDL, приобрели вкус писания на ассемблере и разобрались с организацией простейшего конвейерного микропроцессора, а также как все это стыкуется с периферийными устройствами и встроенным программированием. Что делать дальше?

На снимке — Татьяна Волкова, сотрудница образовательных программ компании Samsung в Московском Физико-Техническом Институте

Читать полностью »