Вчера мне пришло письмо от десятиклассницы из Сибири, которая хочет стать разработчицей микропроцессоров. Она уже получила некоторый результат в этой области — добавила инструкцию умножения в простейший процессор schoolMIPS, синтезировала его для ПЛИС Intel FPGA MAX10, определила максимальную частоту и повышение производительности простых программ. Все это она сначала делала в деревне Бурмистрово Новосибирской Области, а потом на конференции в Томске.

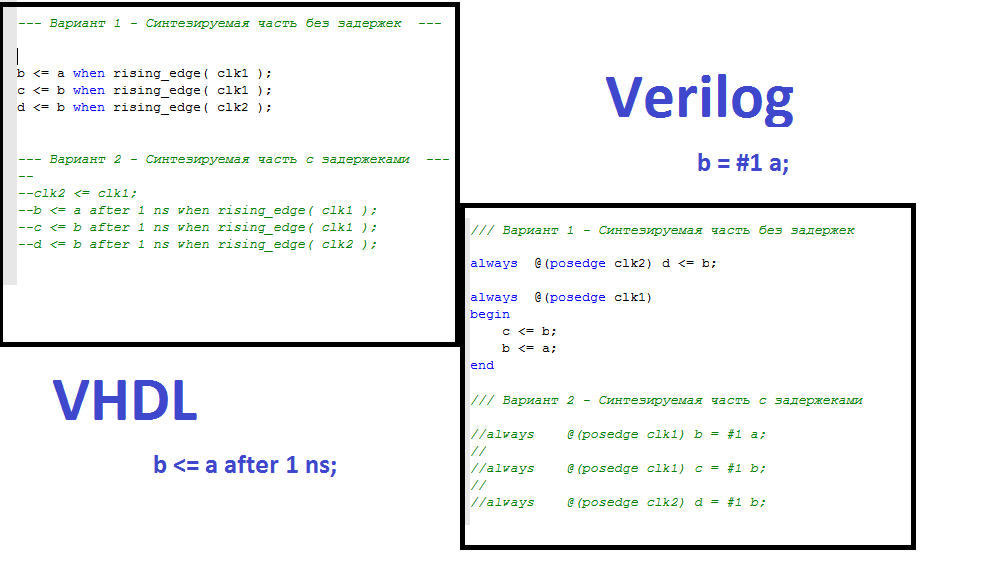

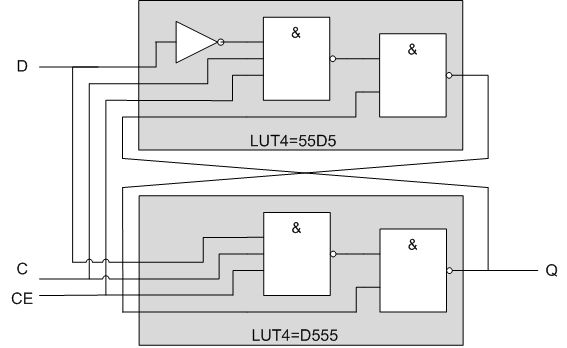

Теперь Даша Криворучко (так зовут десятиклассницу) переехала жить в московский интернат и спрашивает у меня, чего бы ей еще спроектировать. Я думаю, что на этом этапе карьеры ей стоит спроектировать аппаратный ускоритель нейросетей на основе систолического массива для умножения матриц. Использовать язык описания аппаратуры Verilog и ПЛИС Intel FPGA, но не дешевенький MAX10, а что-нибудь подороже, чтобы вместить большой систолический массив.

После этого сравнить производительность аппаратного решения с программой, работающей на процессоре schoolMIPS, а также с программой на Питоне, работающей на десктопном компьютере. В качестве тестового примера использовать распознавание цифр с небольшой матрицы.