Рубрика «vhdl»

СДВИГОВЫЙ РЕГИСТР ИЛИ ТО, О ЧЕМ НЕ РАССКАЖУТ В СТАТЬЯХ ДЛЯ НАЧИНАЮЩИХ :: АТРИБУТЫ СИНТЕЗА

2024-11-28 в 2:44, admin, рубрики: fpga, shift register, Verilog, vhdl, ПЛИС, синтезСдвиговый регистр – это одна из наиболее часто применяемых конструкций в проектах на ПЛИС. Сегодня мы уделим внимание тому, как можно и нужно писать VHDL и Verilog код для сдвиговых регистров, но при этом, чтобы синтезатор понял, что мы хотим реализовать сдвиговый регистр из нескольких триггеров или же задействовать для его реализации специальные ресурсы, такие как SRL регистры.

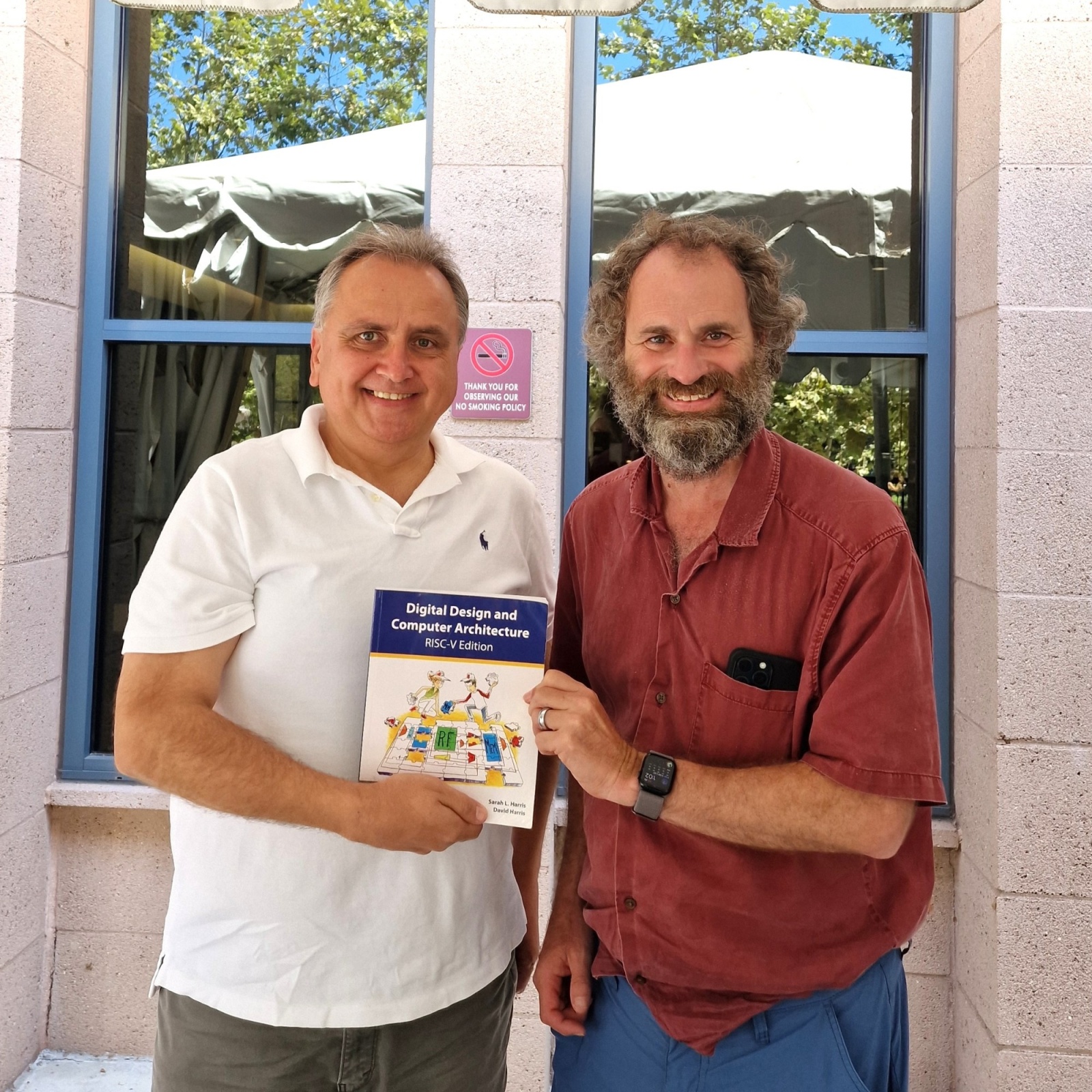

Дэвид Харрис, автор «Цифровой схемотехники и архитектуры компьютера», ответил на вопросы про его следущую книгу и вообще

2024-09-24 в 14:20, admin, рубрики: asic, fpga, maker faire, Verilog, verilog meetup, vhdl, Процессоры, харрис & харрис, цифровая схемотехника, школа синтеза цифровых схем

Встретился на ланч с Дэвидом Харрисом, автором (вместе с Сарой Харрис) популярного учебника Читать полностью »

Детей недостаточно учить только питону и ардуине

2024-06-29 в 17:08, admin, рубрики: 7400, cmos 4000, Gowin, Verilog, vhdl, макетная платаДетей недостаточно учить только питону и ардуине. Нужно еще и цифровой схемотехнике, причем не на симуляторе, так как он для ребенка неубедителен, а на микросхемах малой степени интеграции, лучше которых для иллюстрации функции D-триггера никто с 1968 года ничего не придумал.

Второй номер народного FPGA журнала! «Погоди-ка, а когда был анонс первого?»

2024-05-29 в 5:55, admin, рубрики: fpga, RTL, SystemVerilog, Verilog, vhdl, верификация, журналПЛИС-культ привет, FPGA хабрунити.

На днях состоялся анонс уже второго номера народного FPGA журнала

FPGA-Systems Magazine :: № BETA (state_1). В нем 200+ страниц и 20+ статей и небольших заметок по направлениям FPGA / RTL / Verification (ПЛИС сегодня это не только про знание HDL и Vivado c Quartus'ом). Журнал бесплатный и распространяется в виде pdf-ки.

Зачем? Есть же хабр!

ASIC и FPGA: сорок лет эволюции

2023-12-15 в 9:37, admin, рубрики: asic, Electronic Design Automation, fpga, SystemVerilog, Verilog, vhdl, История микроэлектроникиВнутри каждого современного телефона несколько микросхем ASIС. Ими наполнены автомобили, стойки в центрах обработки данных, датчики «умного дома», и вообще все электронные устройства. Без чипов ASIC был бы невозможен быстрый интернет, трехмерные игры и ускорители машинного обучения.

Слышали ли вы про язык «e»? А ведь он был продан за $315 миллионов долларов

2023-03-24 в 7:08, admin, рубрики: constraint programming, fpga, functional coverage, Hardware Verification Language, Specman, SystemVerilog, SystemVerlog Assertions, Vericity, vhdl, Анализ и проектирование систем, верификация микросхем, программирование микроконтроллеров, Производство и разработка электроники, функциональное программирование, Школа Синтеза

Все знают про язык программирования C, поменьше — про язык программирования F, кое‑кто про B, предшественник C, а вот знаете ли вы про язык «e»? Их кстати два — один с большой буквы «E», а другой с маленькой «e».

Жуткий сценарий использования ChatGPT

2023-02-03 в 18:11, admin, рубрики: asic design, chatgpt, fpga, high-level synthesis, logic synthesis, OpenAI, SystemVerilog, Verilog, vhdl, будущее здесь, искусственный интеллект, Компиляторы, Питон, Производство и разработка электроники

Вчера у меня в ленте на фейсбуке (жаль что в закрытом посте) проявился еще один аспект ChatGPT, жуть которого я не вполне осознавал. Представьте, что ваш менеджер присылает вам емейл: "я вот тут сгенерил с помощью ChatGPT код на языке описания аппаратуры SystemVerilog, который реализует мою идею, ты его поправь немного и в продакшн, а то нас сроки поджимают".