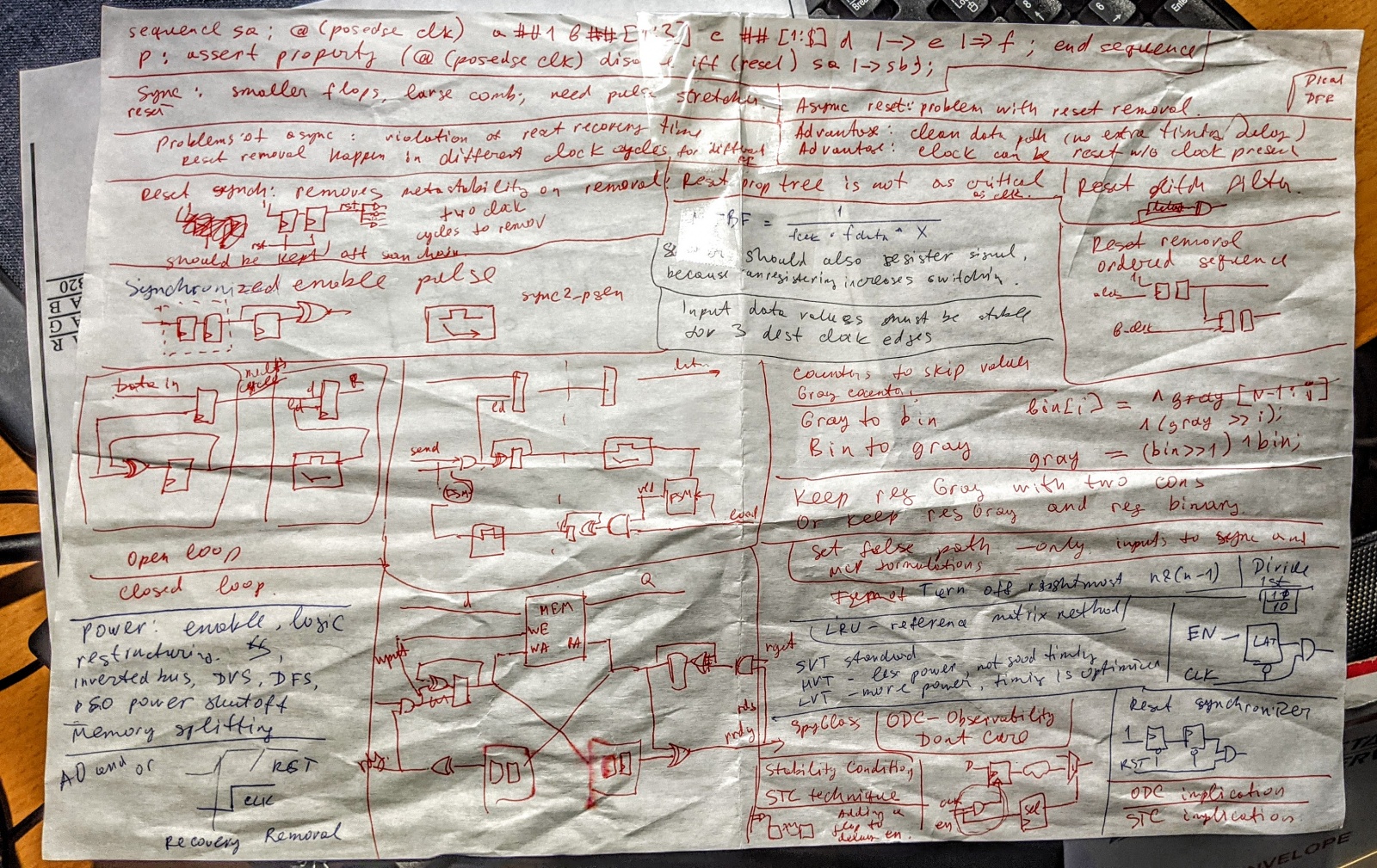

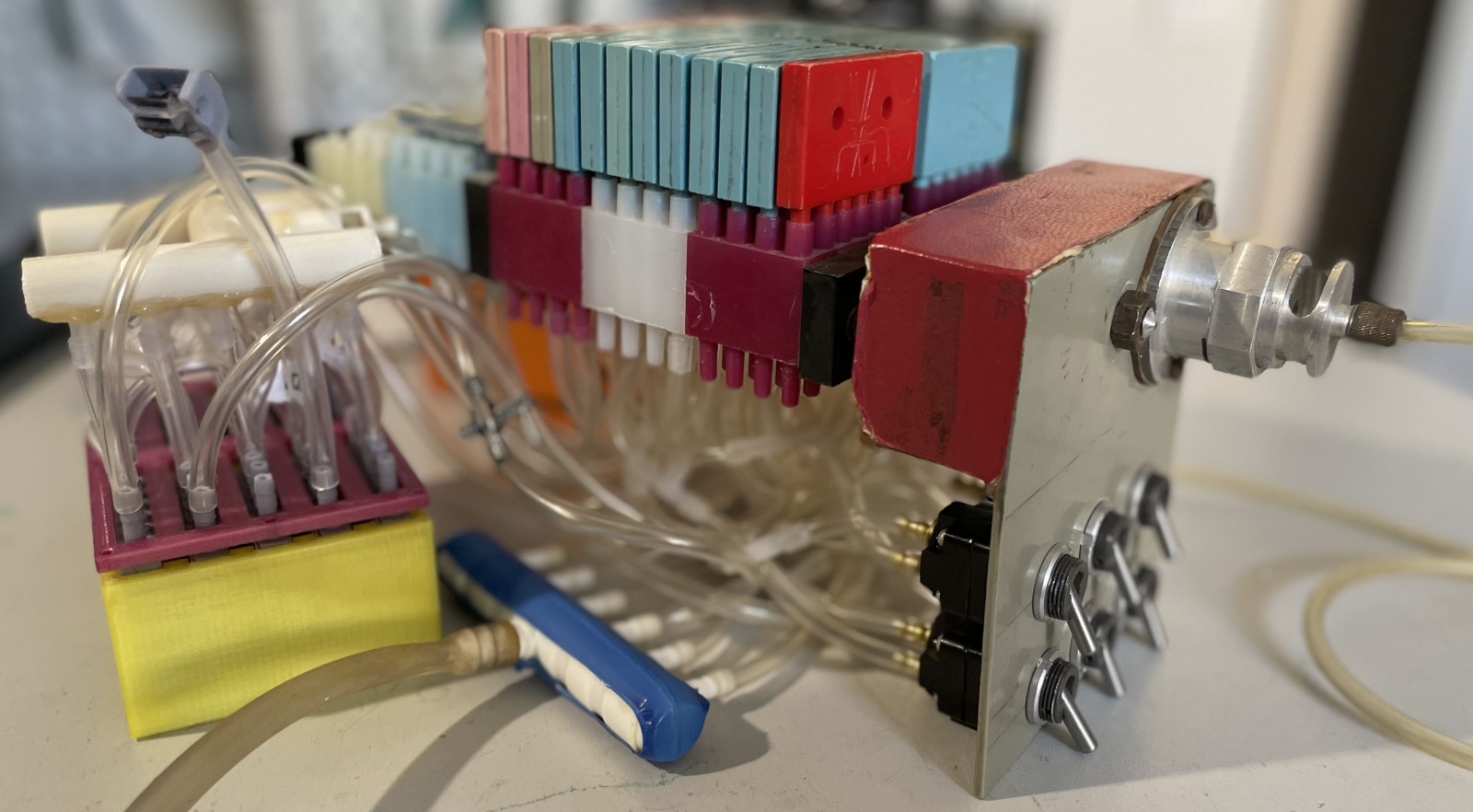

Проектируемый компьютер на сверхминиатюрных электронных лампах хоть и является радиационно-стойким, однако работает на электричестве. Кроме того, восстановить в сжатые сроки производство электронных ламп в условиях постапокалипсиса будет довольно сложной задачей. На руинах цивилизации гораздо проще организовать массовое производство логических элементов, работающих на эффекте прилипания струи воздуха к стенке — при этом сам элемент можно лепить хоть из глины! И мало того, что для создания потока воздуха не обязательно использовать электричество — теоретически такой процессор сможет работать на энергии ударной волны ядерного взрыва! Но обо всём по порядку. Для тех, кто следит за проектом DekatronPC — не пугайтесь, ему ничего не угрожает.

В прошлый раз в статье «Пневмоника и влажные мечты стимпанка» я уже рассказывал о струйных логических элементах и поделился мыслями о том, что в принципе на этой технологии можно собрать полноценное вычислительное устройство. Читать полностью »