Третий ежегодный слет hardware-инженеров пройдет в Москве уже через месяц, 29 ноября. Мы расширили целевую аудиторию: в программе найдется интересное не только для мастеров FPGA, но и для RTL-шаманов, гуру верификации и адептов физического дизайна. А еще будут DIY-стенды с «железками» от комьюнити! Больше подробностей — далее в посте.

Рубрика «верификация микросхем»

Шестнадцать (sic!) докладов про «железо» за один день: FPGA-Systems 2025 у порога

2025-10-24 в 11:17, admin, рубрики: fpga-systems, RTL, верификация микросхем, ПЛИС, физический дизайнПуть в микроэлектронику через верификацию: руководство для начинающих

2025-04-10 в 11:34, admin, рубрики: soc design, верификация, верификация микросхем, производство электроникиПривет! Меня зовут Дмитрий Кишко, я руководитель группы функциональной верификации в YADRO. Представьте, что вы строите космический корабль. Он еще не взлетел, но любая ошибка в конструкции уже может стоить миллионы или даже сорвать всю миссию. В мире микроэлектроники ситуация похожа: перед тем как чип попадет на производство, его работу проверяют сотни раз, но не физически, а в симуляторах. Этот этап называется функциональной верификацией, и без него современная электроника просто «не взлетит».

Слышали ли вы про язык «e»? А ведь он был продан за $315 миллионов долларов

2023-03-24 в 7:08, admin, рубрики: constraint programming, fpga, functional coverage, Hardware Verification Language, Specman, SystemVerilog, SystemVerlog Assertions, Vericity, vhdl, Анализ и проектирование систем, верификация микросхем, программирование микроконтроллеров, Производство и разработка электроники, функциональное программирование, Школа Синтеза

Все знают про язык программирования C, поменьше — про язык программирования F, кое‑кто про B, предшественник C, а вот знаете ли вы про язык «e»? Их кстати два — один с большой буквы «E», а другой с маленькой «e».

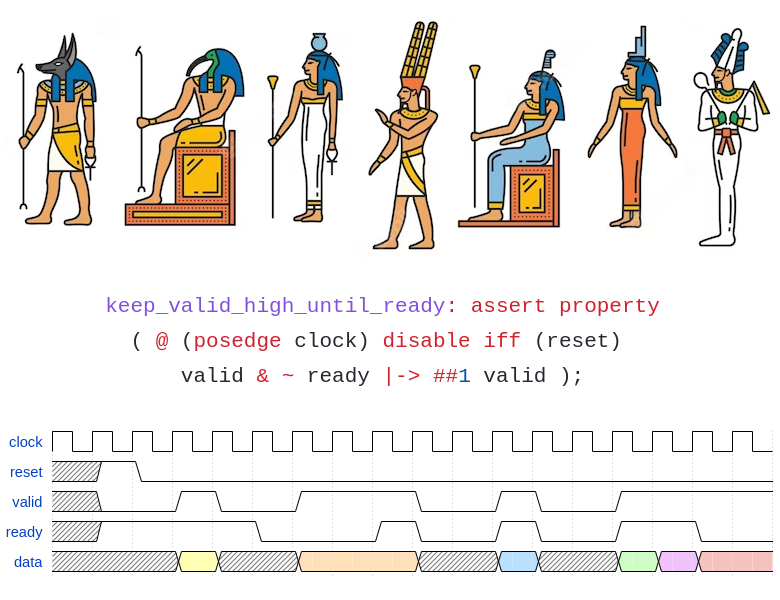

Темное искусство функциональной верификации цифровых микросхем

2022-02-26 в 8:26, admin, рубрики: asic, constraint programming, fpga, functional coverage, simulation, SystemVerilog, verification, Verilog, Алгоритмы, Анализ и проектирование систем, верификация микросхем, математика, Производство и разработка электроники, темпоральная логикаСегодня, в субботу 26 февраля, на Сколковской Школе Синтеза Цифровых Схем Михаил Коробков проводит занятие по технологиям функциональной верификации: constrain solvers, cover bins и concurrent assertions. Примеры, которые мы подготовили для школы, вращаются вокруг протокола AXI для систем на кристалле, вопросы про который спрашивают например на интервью в хардверное отделение компании Meta и другие.