Новость для тех, кто хочет сделать начало следующего года особенным для своего развития. Второй год мы запускаем бесплатные практические курсы по востребованным инженерным направлениям. К уже классическим трекам по верификации, DevOps и Go-разработке добавился новый: «Программирование микроконтроллеров RISC-V: от основ работы с открытой архитектурой до создания собственного устройства». РегистрируйтесьЧитать полностью »

Рубрика «верификация»

Разработка на Go, верификация, DevOps и программирование микроконтроллеров на RISC-V: выбирай бесплатный курс

2024-12-13 в 13:39, admin, рубрики: devops, Go, risc-v, верификация, курсыПроектирование RTL на SCALA, схемотехника в российских САПР и верификация RISC-V: 8 докладов заключительной FPGA Systems

2024-11-25 в 14:00, admin, рубрики: asic, fpga, fpga-systems, RTL, rtl-дизайн, SoC, верификация, конференцияЕсли вы хотя бы раз слушали доклады FPGA Systems, вы знаете, что это настоящий интенсив с новыми знаниями по FPGA-разработке и не только. Заключительная конференция сообщества в этом году, организованная с YADRO, — не исключение. 30 ноября, в субботу, вас ждет восемь докладов от инженеров из МИЭТ, БЮРО 1440, ЭРЕМЕКС, YADRO. От новостей китайских ПЛИС (BMTI) — докладчик недавно посетил их производство — до разбора практических кейсов. Например, как запустить видеокарту AMD на ПЛИС с RISC-V.

Места на офлайн уже разобрали, но онлайн-трансляция доступна всем. Изучайте программу и подключайтесь к интересному именно вам докладу. И обязательно Читать полностью »

Второй номер народного FPGA журнала! «Погоди-ка, а когда был анонс первого?»

2024-05-29 в 5:55, admin, рубрики: fpga, RTL, SystemVerilog, Verilog, vhdl, верификация, журналПЛИС-культ привет, FPGA хабрунити.

На днях состоялся анонс уже второго номера народного FPGA журнала

FPGA-Systems Magazine :: № BETA (state_1). В нем 200+ страниц и 20+ статей и небольших заметок по направлениям FPGA / RTL / Verification (ПЛИС сегодня это не только про знание HDL и Vivado c Quartus'ом). Журнал бесплатный и распространяется в виде pdf-ки.

Зачем? Есть же хабр!

Будущее математики?

2020-07-18 в 18:47, admin, рубрики: lean, будущее здесь, будущее математики, верификация, доказательство, искусственный интеллект, математика, Научно-популярное, формальное доказательствоВ этом переводе презентации британского математика Кевина Баззарда мы увидим, что следующий комикс xkcd безнадежно устарел.

Каково будущее математики?

- В 1990-х компьютеры стали играть в шахматы лучше людей.

- В 2018 компьютеры стали играть в го лучше людей.

- В 2019 исследователь искусственного интеллекта Christian Szegedy сказал мне, что через 10 лет компьютеры будут доказывать теоремы лучше, чем люди.

Конечно, он может быть не прав. А может быть и прав.

Читать полностью »

Имитационная модель процесса обработки материала резанием на токарном станке с ЧПУ

2020-02-19 в 14:10, admin, рубрики: CAD/CAM, fanuc, gcode, simulator, WebGL, верификация, код, математика, обеспечение, обработка, обучение, программа, Программирование, проектирование, симулятор, система, Софт, стандарт, станок, технология, токарный, управление, формообразование, цикл, чпуВведение

Методология разработки имитационных моделей и симуляторов по различным техническим дисциплинам в основном ориентирована на снижение уровня абстракции учебного материала. Наряду с теоретическим учебным материалом наглядное имитационное моделирование того или иного технологического процесса или операции позволяет учащемуся в более полной мере освоить преподаваемый материал с максимальным приближением к естественным условиям. При этом имитационные модели и симуляторы могут рассматриваться только как вспомогательный инструмент учебного процесса. Основное назначение данной категории образовательных ресурсов – базовое (начальное) ознакомление с принципами работы сложных технических объектов в условиях отсутствия возможности использования реального промышленного оборудования, либо в целях предварительного повышения компетенции учащегося перед прохождением производственной практики.

Читать полностью »

Использование верилятора как средства быстрого моделирования RTL проектов. Введение в UVM

2019-07-09 в 12:03, admin, рубрики: Accelera, c++, gtkwave, modelsim, RTL, systemc, UVM, verilator, Verilog, верификация, Компиляторы, Производство и разработка электроники, СофтВ данной статье будут описаны установка и применение бесплатного ПО для моделирования схем цифровой логики на языке Verilog как альтернативы коммерческих продуктов Incisve от компании Cadense и ModelSim от компании MentorGraphics. Сравнение моделирования в ModelSim и Verilator. Так же будет рассмотрена универсальная методолгия верификации — UVM.

Установка ПО для SystemC UVM

1. Верилятор

Одним из языков описания аппаратуры является verilog. На этом языке можно написать модуль.

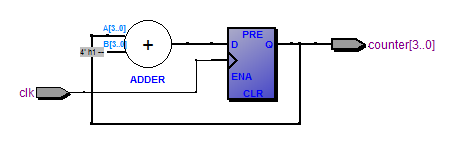

Например, есть схема счетика:

Его код будет выглядеть так:

reg [3:0]counter;

always @(posedge clk or posedge reset)

if(reset)

counter <= 4'd0;

else

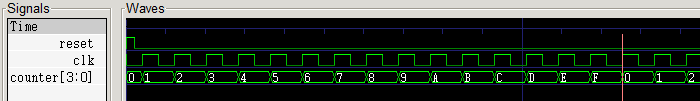

counter <= counter + 1'd1;После симуляции получим вейвформы:

Видно, что по фронту тактовой частоты в регистры счетчика будет записываться очередное значение, на единицу большее, чем предыдущее.

Написанный модуль может иметь и более сложную структуру, проверить все состояния которого вручную будет сложно. Нам понадобится автоматизированное тестирование. Для этого необходимо разработать тестовое окружение на одном из языков программирования. Тестовое окружение даст нам возможность провести полную функциональную проверку устройства.

Для тестирование кода проекта помимо таких языков как Verilog, SystemVerilog, Python (для написания моделей), можно использовать язык SystemC. SystemC — язык проектирования и верификации моделей системного уровня, реализованный в виде C++ библиотеки с открытым исходным кодом.

Один из способов верификации Verilog модулей с помощью SystemC является трансляция verilog файлов в С++. Поможет нам в этом Verilator.

Verilator — это самый быстрый бесплатный симулятор Verilog HDL, который превосходит большинство коммерческих симуляторов. Verilator компилирует синтезируемый SystemVerilog (обычно это не код тестового стенда), а также некоторые утверждения SystemVerilog и Synthesis в однопоточный или многопоточный код C ++ или SystemC. Verilator был разработан для больших проектов, где быстродействие симуляции имеет первостепенное значение, и особенно хорошо подходит для генерации исполняемых моделей процессоров для групп разработчиков встроенного программного обеспечения. Verilator используется для имитации многих очень больших многомиллионных конструкций шлюзов с тысячами модулей и поддерживается многими поставщиками IP-технологий, включая IP от Arm и всех известных поставщиков RISC-V IP.

Читать полностью »

Сложные базы данных

2019-05-30 в 15:33, admin, рубрики: big data, data mining, nosql, sql, базы данных, верификация, Модель данных, поиск информации, ПрограммированиеО том, что объёмы данных, сложность их структуры, сложность связей между ними растут совершенно невероятными темпами, пишут на каждом заборе уже много лет. Вопрос же о том, что делать со всей этой свалкой обычно повисает в воздухе. Или, точнее, упирается в понятие «модель данных».Читать полностью »

Верификация фотографий в ритейле с помощью Computer vision

2018-12-18 в 16:47, admin, рубрики: computer vision, Блог компании Tinkoff.ru, верификация, глубокое обучение, машинное обучение, обработка изображенийВступление

В рамках программы кредитования банк сотрудничает со многими розничными магазинами.

Одним из ключевых элементов заявки на кредит является фотография заемщика – агент магазина-партнера фотографирует покупателя; такая фотография попадает в «личное дело» клиента и используется в дальнейшем как один из способов подтверждения его присутствия на точке в момент подачи заявки на кредит.

К сожалению, всегда существует риск недобросовестного поведения агента, который может передавать в банк недостоверные фотографии – например, снимки клиентов из социальных сетей или паспорта.

Обычно банки решают эту задачу с помощью верификации фотографии – сотрудники офиса просматривают фотографии и пытаются выявить недостоверные изображения.

Мы захотели попробовать автоматизировать процесс и решить задачу с помощью нейросетей.

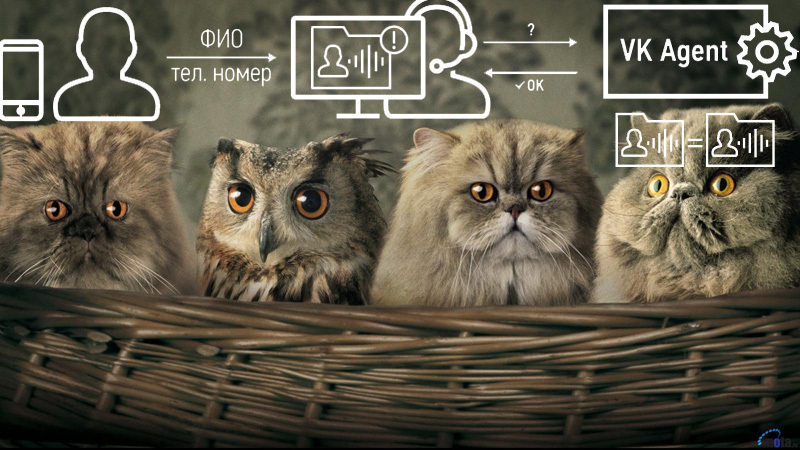

Голосовые «отпечатки» теперь официально работают (и как выглядит процесс внедрения в Приорбанке)

2016-08-11 в 7:33, admin, рубрики: Анализ и проектирование систем, аутентификация пользователей, банк, Блог компании КРОК, верификация, голосовая биометрия, голосовой отпечаток, звук, идентификация, информационная безопасность, метки: голосовая биометрия

— А не западло ли вам там в банке отвечать на анонимные вопросы?

— Нет, Владимир Петрович, не западло.

Один из крупнейших коммерческих банков Беларуси Приорбанк, входящий в австрийскую группу «Райффайзен», использует голосовые эталоны (или, как ещё говорят, голосовые «отпечатки») клиентов для подтверждения их личности при обращении по телефону. Это пока только второй случай на территории России и СНГ, когда банк официально заявил о факте использования такой технологии.

Про саму голосовую биометрию мы уже рассказывали (возможность «узнавания» и определения личности звонящего, например в контакт-центр абонента, даже если он использует другой телефон или представляется кем-то другим — это актуально для антифрода). Расскажу о том, какие особенности есть во внедрении голосовой биометрии на примере Приорбанка.Читать полностью »