Некоторое время назад мне в очередной раз потребовался USB-Serial адаптер. И не просто адаптер c RX/TX, а чтобы еще присутствовали управляющие сигналы. И не один UART, а несколько. И еще желательно, в виде одного композитного устройства, чтобы все это хозяйство не занимало больше одного USB-порта. Так и началась эта история...

Рубрика «uart» - 3

Полноценный трехпортовый USB-Serial адаптер на STM32 Blue Pill (STM32F103C8T6)

2020-11-27 в 10:26, admin, рубрики: arm-none-eabi, CDC, CMSIS, composite device, open source, Open Source Software, serial port, stm32, stm32f103, uart, usb, программирование микроконтроллеровОткрытие портов 4321 и 9898 на шлюзе Xiaomi Gateway 2

2020-02-10 в 12:56, admin, рубрики: home assistant, uart, xiaomi, умный дом, шлюзВведение

Отдыхая на новогодних праздниках, я загорелся идеей создания «Умного дома». Среди «народных» экосистем наиболее популярным в силу дешевизны и обилия всевозможных подключаемых устройств мне сразу показалось решение от Xiaomi. Сразу отказавшись от управления своим домом через китайские сервера (возможные задержки, безопасность и привязка к устройствам одного производителя), я принялся изучать всевозможные системы управления умным домом и подбирать для них совместимое оборудование.

После часов поисков я решил, что мне подходит Home Assistant. Строить всё на начальном этапе я решил с использованием Raspberry Pi 4 Model B (2GB) и датчиков от Xiaomi. Купив шлюз (нужна версия с артикулом DGNWG02LM) и включив протокол связи локальной сети, я столкнулся с тем, что порты 4321 и 9898, необходимые для интеграции в Home Assistant, по-прежнему остались закрытыми.

Читать полностью »

Простой USB-UART преобразователь с гальванической развязкой

2019-11-29 в 12:29, admin, рубрики: cp2102, debug, diy или сделай сам, uart, usb, изолятор, программирование микроконтроллеров, Производство и разработка электроники, схемотехника, Электроника для начинающихВ процессе разработки электронных устройств под управлением микроконтроллеров, часто возникает задача передать какие-то данные с устройства на компьютер или наоборот. Вероятно самым простым способом является использование USB-UART переходников, которых существует великое множество, но я решил сделать свой «велосипед» и поделиться результатом с вами.

У меня стояла задача сделать для себя любимого простой, дешевый, компактный и главное гальванически развязанный преобразователь USB-UART. Основной кейс для меня — отладка через printf по uart, да да, я в курсе про SWO и иные методы, но мне удобнее работать именно с uart-ом. Наличие изоляции для меня критично, т.к. в основном мне приходится проектировать силовые преобразователи, которые могут легко спалить, например, usb порт моего ноутбука. Правда если у вас в устройствах нет высокого напряжение, то расслабляться тоже не стоит, какие-нибудь 12В так же прекрасно могут вывести из строя ваш ПК. Разумеется не стоит забывать и о помехах, гальваническая развязка частично препятствует попаданию всякой гадости в usb порт.

Как видите у развязанных преобразователей интерфейсов одни плюсы, но тут некоторые возразят: «Зачем? Все же есть на Алиэкспресс». Тут ответ простой — меня не устроили ни цена готового устройства, ни его габариты, ни качество. В итоге за пару часов я «изобрел велосипед», который удовлетворит все мои хотелки и после изготовления получилось вот так:

Хотите обезопасить свои usb порты и узнать зачем так много? Тогда поехали :))

Читать полностью »

uJVM: platform for running Java applications on microcontrollers (MCUs)

2019-07-09 в 13:10, admin, рубрики: arduino, avr, crypto, gpio, hello world, java, jvm, mcu, msp432, open source, saml, stm32, systick, tm4c1294, uart, Программирование, программирование микроконтроллеров Hello dear readers. In this article I will try to demonstrate how to run a Java Virtual Machine and Java applications on microcontrollers. This idea may sound quite outlandish by itself: why use Java on microcontrollers where each byte of RAM and each CPU cycle are precious commodity? There's nothing like native C for microcontrollers — even C++ is rarely used! Yes, I've heard that discussion (and took part in it) for many years. Well, I will try to explain «why», as well as «how», in this article. So, anyone who wants to understand how MCU implementation of JVM works; see an unusual approach to multi-platform project development; take part in Open Source project; or just have fun — welcome onboard, uJVM is ready to take off! People who are ready to criticize can stay near the runway and watch us climb (or crash) from a safe distance

Hello dear readers. In this article I will try to demonstrate how to run a Java Virtual Machine and Java applications on microcontrollers. This idea may sound quite outlandish by itself: why use Java on microcontrollers where each byte of RAM and each CPU cycle are precious commodity? There's nothing like native C for microcontrollers — even C++ is rarely used! Yes, I've heard that discussion (and took part in it) for many years. Well, I will try to explain «why», as well as «how», in this article. So, anyone who wants to understand how MCU implementation of JVM works; see an unusual approach to multi-platform project development; take part in Open Source project; or just have fun — welcome onboard, uJVM is ready to take off! People who are ready to criticize can stay near the runway and watch us climb (or crash) from a safe distance

uJVM: платформа для запуска Java-приложений на микроконтроллерах (MCU)

2019-07-04 в 7:18, admin, рубрики: arduino, avr, crypto, gpio, hello world, java, jvm, mcu, msp432, open source, saml, stm32, systick, tm4c1294, uart, программирование микроконтроллеров Добрый день, уважаемыее. В этом цикле статей я попытаюсь рассказать Вам о Java Virtual Machine и запуске Java программ на микроконтроллерах. Тема достаточно спорная: Зачем Java на микроконтроллерах, где и так мало ресурсов? Лучше нативного кода написаного на чистом С, ничего нет, даже на плюсах мало кто пишет! И т.д. Сразу скажу, сам задавал себе эти вопросы и не один раз. Мой ответ такой: Кто хочет попробовать, на что способно железо; понять, как работает JVM; увидеть интересный подход к построению мультиплатформенного проекта; внести свой вклад в Open Source; или просто побаловаться — все на борт, корабль по имени uJVM отправляется в плавание! Те кто уже настроился критиковать, смотрите как «Титаник» отправился в путь, надеюсь на Вашу лояльность!

Добрый день, уважаемыее. В этом цикле статей я попытаюсь рассказать Вам о Java Virtual Machine и запуске Java программ на микроконтроллерах. Тема достаточно спорная: Зачем Java на микроконтроллерах, где и так мало ресурсов? Лучше нативного кода написаного на чистом С, ничего нет, даже на плюсах мало кто пишет! И т.д. Сразу скажу, сам задавал себе эти вопросы и не один раз. Мой ответ такой: Кто хочет попробовать, на что способно железо; понять, как работает JVM; увидеть интересный подход к построению мультиплатформенного проекта; внести свой вклад в Open Source; или просто побаловаться — все на борт, корабль по имени uJVM отправляется в плавание! Те кто уже настроился критиковать, смотрите как «Титаник» отправился в путь, надеюсь на Вашу лояльность!

Удалённое управление UART’ом через Web

2019-02-15 в 14:36, admin, рубрики: django, ReactJS, remote monitoring, uart, Интернет вещей, облачные сервисы, Производство и разработка электроникиНачнём с железа

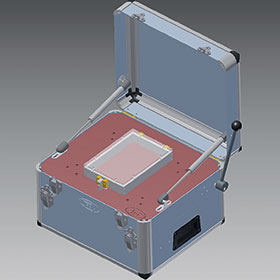

Работал я как-то на одном заводе, где лепили всякую электронику, не шибко сложную, и иногда подпадавшую под определение «Интернет вещей». По большей части, всякие датчики для охранных систем: датчики дыма, шума, проникновения, огня и всякое другое. Ассортимент изделий был широчайший, партии иногда были меньше 500 штук, и едва ли не под каждое изделие приходилось делать отдельный Test Fixture — по сути, просто жестяная коробка, в которую изделие на тестах ставилось, прижималось крышкой, и снизу контактные иглы прижимались к контактным точкам на печатной плате, как-то так:

Работал я как-то на одном заводе, где лепили всякую электронику, не шибко сложную, и иногда подпадавшую под определение «Интернет вещей». По большей части, всякие датчики для охранных систем: датчики дыма, шума, проникновения, огня и всякое другое. Ассортимент изделий был широчайший, партии иногда были меньше 500 штук, и едва ли не под каждое изделие приходилось делать отдельный Test Fixture — по сути, просто жестяная коробка, в которую изделие на тестах ставилось, прижималось крышкой, и снизу контактные иглы прижимались к контактным точкам на печатной плате, как-то так:

Читать полностью »

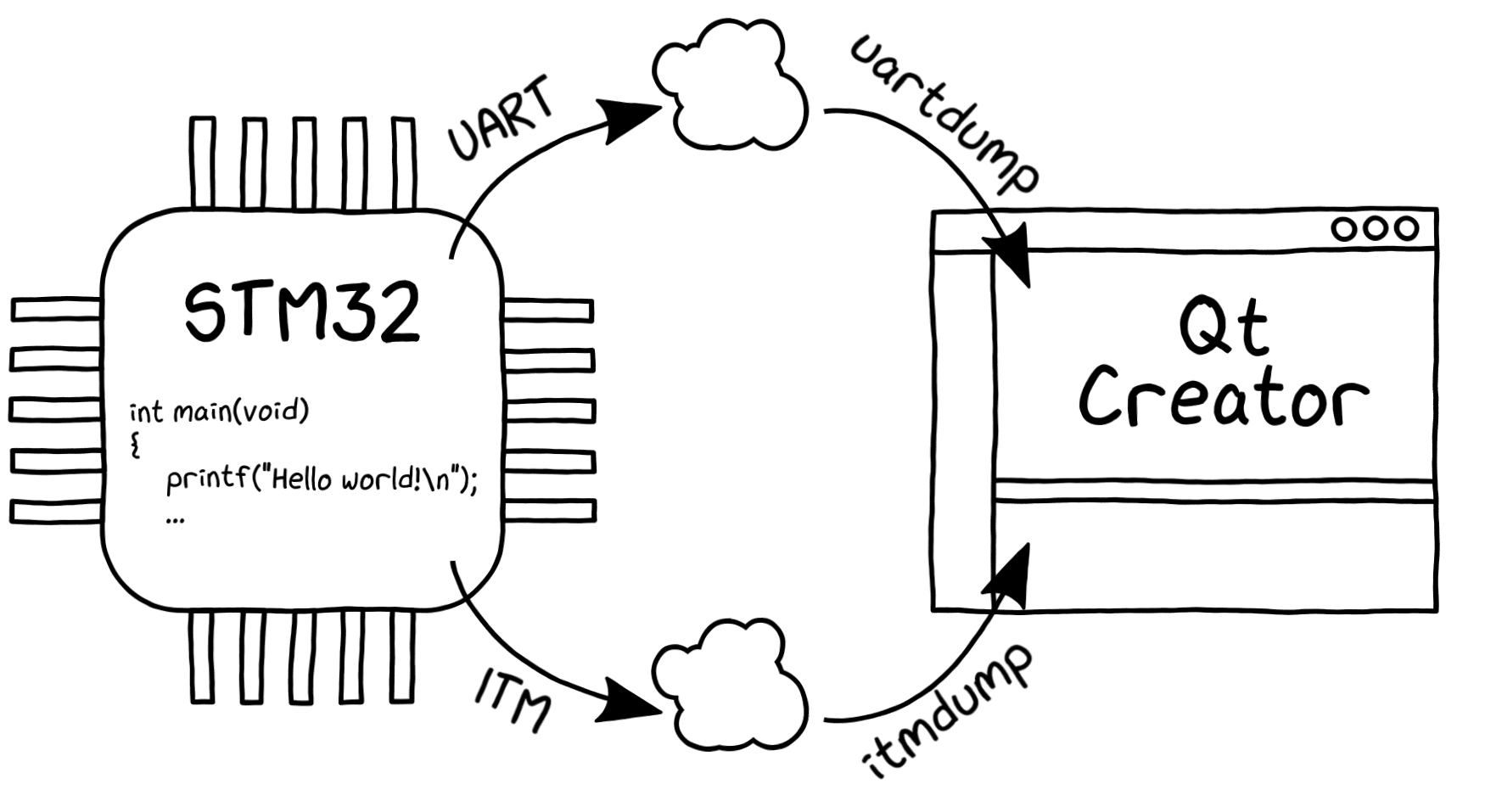

Перенаправляем printf() из STM32 в консоль Qt Creator

2019-02-12 в 12:57, admin, рубрики: debug, itm, printf, qt creator, retarget, stm32, swo, uart, программирование микроконтроллеров

Нередко при отладке ПО микроконтроллера возникает необходимость вывода отладочных сообщений, логов, захваченных данных и прочего на экран ПК. При этом хочется, чтобы и вывод был побыстрее, и чтобы строки отображались не где-нибудь, а прямо в IDE — не отходя от кода, так сказать. Собственно, об этом и статья — как я пытался printf() выводить и отображать внутри любимой, но не очень микроконтроллерной, среды Qt Creator.

RS-485 на отечественных микроконтроллерах от фирмы Миландр

2019-02-08 в 9:50, admin, рубрики: 1986ве1, 1986ве91т, RS-486, uart, боль и унижение, миландр, программирование микроконтроллеров, Электроника для начинающих

Несколько дней назад я имел неосторожность завуалированно пообещать запилить пост про Миландр… Ну что ж, попробуем.

Как вы, вероятно, уже знаете, существует российская компания Миландр, которая, среди прочего, выпускает микроконтроллеры на ядре ARM Cortex-M. Волею судеб я был вынужден с ними познакомиться достаточно плотно, и познал боль.

Небольшая часть этой боли, вызванная работой с RS-485, описана далее. Заранее прошу прощения, если слишком сильно разжевываю базовые понятия, но мне хотелось сделать эту статью доступной для понимания более широкой аудитории.

Так же заранее оговорюсь, что имел дело только с 1986ВЕ91 и 1986ВЕ1, о других уверенно говорить не могу.

Мой «Hello World!» на FPGA или очередная версия UART

2018-10-19 в 12:29, admin, рубрики: Altera, diy или сделай сам, fifo, fpga, IP CORE, LPM_ALTPLL, LPM_COUNTER, MEGAFUNCTIONS, PLL, Quartus, rs-232, uart, Verilog, мажоритарный элемент, ПЛИС, Программирование, прототипирование, схемотехника

Наконец-то у меня дошли руки до изучения ПЛИС. А то как-то неправильно получается: драйвера на железо под Linux пишу, микроконтроллеры программирую, схемы читаю (и немного проектирую), надо расти дальше.

Так как мигать светодиодами мне показалось не интересно, то решил сделать простенькую вещь. А именно написать модули приемника и передатчика для UART, объединить их внутри FPGA (заодно понять как использовать IP Core), ну и протестировать это все на реальном железе.

Читать полностью »

Конференция DEFCON 22. Группа GTVHacker. Взламываем всё: 20 устройств за 45 минут. Часть 2

2018-10-04 в 10:13, admin, рубрики: uart, Блог компании ua-hosting.company, Взлом устройств, взлом через карты памяти EMMC, взлом через порты отладки, взлом через серийные порты, информационная безопасность, конференции, старое железоКонференция DEFCON 22. Группа GTVHacker. Взламываем всё: 20 устройств за 45 минут. Часть 1

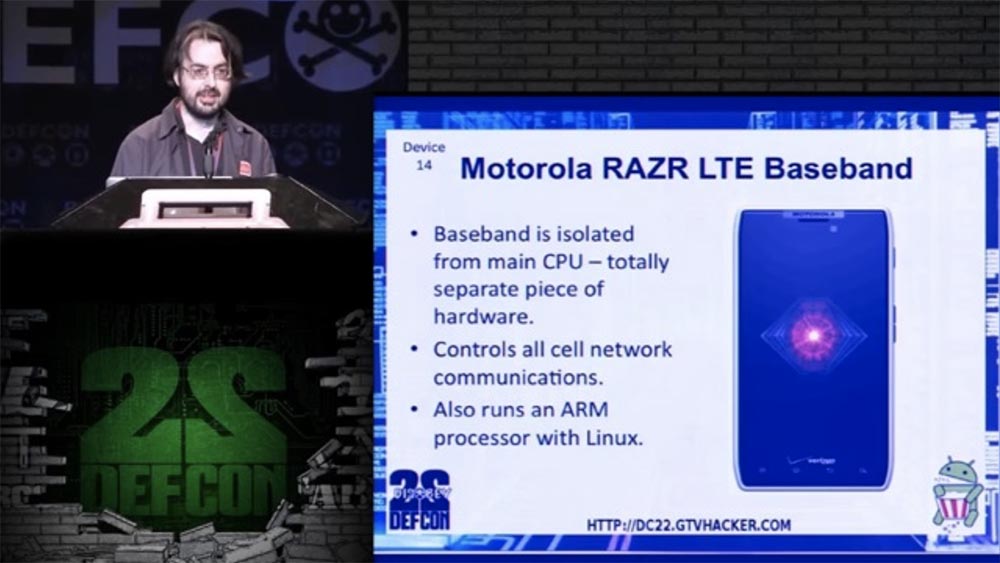

Майк Бейкер: следующее, 14-е устройство, к которому мы получили root-доступ – это смартфон Motorola RAZR LTE Baseband. Я не собираюсь говорить про Android, он уже «прорутован». Этот телефон особенный, так как использует Baseband – отдельный сигнальный процессор, изолированный от основного процессора. Это полностью отдельная часть аппаратного обеспечения смартфона.

Связь между Android и Baseband осуществляется через сетевое USB-подключение. Baseband прослушивает внутренний сетевой порт USB, имеет лимитированный доступ к оболочке через порт 3023 и запускает диагностический скрипт через порт 3002 как root.

Если посмотреть на сценарий, то видно, что с помощью языка AWK запускается команда busybox:

busybox awk '{print+substr(" ' "$ {outFilePath}" ' ",0,1)}’То есть происходит передача имени файла через скрипт AWK. Это означает, что с помощью имени файла мы можем сделать инъекцию в оболочку. Для рутирования оболочки мы используем имя файла, содержащее:

x",0,1);system("…");("Это позволяет вводить в систему любую команду и запускать её с root-правами.Читать полностью »