Linux Foundation открыли новое направление — CHIPS Alliance. В рамках этого проекта организация будет развивать свободную систему команд RISC-V и технологии для создания процессоров на её основе. Расскажем подробнее, что происходит в этой сфере.

Рубрика «risc-v» - 6

Linux Foundation займется open source чипами

2019-03-21 в 10:00, admin, рубрики: hardware, linux foundation, open source, risc-v, Блог компании ИТ-ГРАД, ИТ-ГРАД, ПроцессорыПеренос Alpine Linux на RISC-V

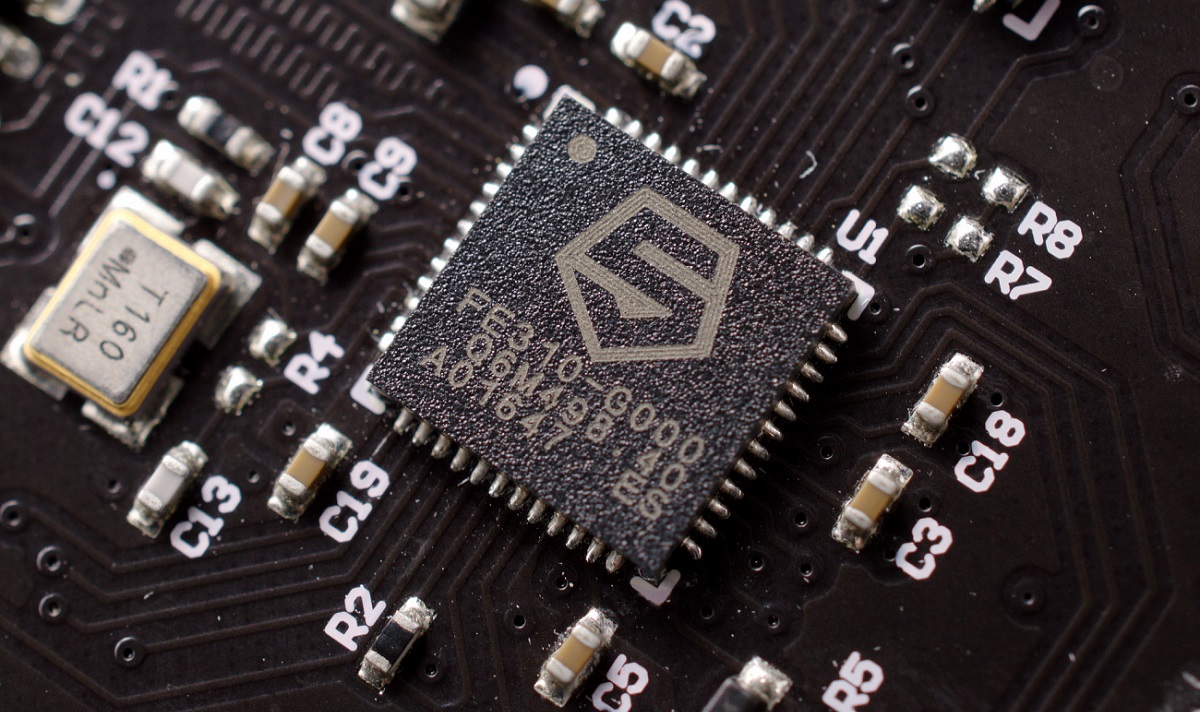

2018-12-25 в 19:11, admin, рубрики: Alpine Linux, HiFive Unleashed, open source, risc-v, Компьютерное железо, Настройка Linux, ПроцессорыПосле нескольких мучительных месяцев ожидания недавно я получил свой HiFive Unleashed, и это невероятно круто. Для тех, кто не в курсе, HiFive Unleashed — это первый одноплатник на RISC-V с поддержкой Linux, ориентированный на потребителя. Если ещё не понятно, RISC-V — это открытая, свободная архитектура набора команд, а HiFive — открытый процессор, реализующий её. И вот он на моём обеденном столе:

Плата реально классная. В течение ближайших месяцев постараюсь подготовить всё необходимое для сервиса непрерывной интеграции builds.sr.ht, через который будет автоматизирована оставшаяся часть переноса Alpine Linux, а также установка любых других операционных систем (в том числе не-Linux) и пользовательских программ, которые вы захотите портировать на RISC-V. Я вполне уверен, что это будет первый подобный проект на оборудовании RISC-V, открытый для публики.

Читать полностью »

Проект Keystone: доверенная среда для запуска приложений на базе RISC-V

2018-09-19 в 18:51, admin, рубрики: keystone, risc-v, анклав, Блог компании ИТ-ГРАД, информационная безопасность, ИТ-ГРАДКоманда исследователей из MIT и Калифорнийского университета в Беркли при поддержке Facebook, Google, Microsoft и других ИТ-гигантов представила проект Keystone. Это open source компонент, позволяющий организовать доверенную среду для запуска программ (trusted execution environment, TEE) на базе архитектуры RISC-V.

Далее — о том, зачем понадобилось решение и как оно устроено.

Генерация и тестирование ядра RISC-V

2018-04-10 в 14:48, admin, рубрики: fpga, open source, parallella, risc-v, zynq, Тестирование IT-системКак я писал в прошлом посте, название моего проекта на GSoC-2016 — «порт RISC-V на Parallella», и первая вещь, которую я должен был сделать, это познакомиться с экосистемой RISC-V. Один из лучших способов это сделать, — посмотреть видео с презентации первого воркшопа RISC-V на Youtube. Для того, чтобы понять самые важные концепции, я рекомендую следующие презентации:

- Введение (Krste Asanović) видео слайды

- Тулчейн RISC-V (Andrew Waterman) видео слайды

- SoC-генератор RISC-V “Rocket Chip” в Chisel (Yunsup Lee) видео слайды

- Структура программного стека RISC-V (Sagar Karandikar) видео слайды

- Отладка на RISC-V (Albert Ou) видео слайды

- Портирование нового кода на RISC-V с OpenEmbedded (Martin Maas) видео слайды

- Окружение тестирования RISC-V (Stephen Twigg) видео слайды

Ещё одна ссылка, если вы интересуетесь Chisel, языком, основанным на Scala, который используется для описания текущей аппаратной реализации ядра RISC-V (ядро Rocket имеет in-order конвейер, BOOM — out-of-order), и любых будущих реализаций.

Краткое руководство по Chisel (Jonathan Bachrach) видео слайды

Работа с Rocket Chip, добавление расширений, инфраструктура ASIC и FPGA (Colin Schmidt) видео слайды

Если вы глубоко заинтересованы в RISC-V и развитии сообщества, я предлагаю вам принять участие в воркшопах.