Некоммерческая организация lowRISC при участии Google и других спонсоров 5 ноября 2019 года представила проект OpenTitan, который называет «первым опенсорсным проектом по созданию открытой, качественной архитектуры микросхем с корнем доверия (RoT) на аппаратном уровне».

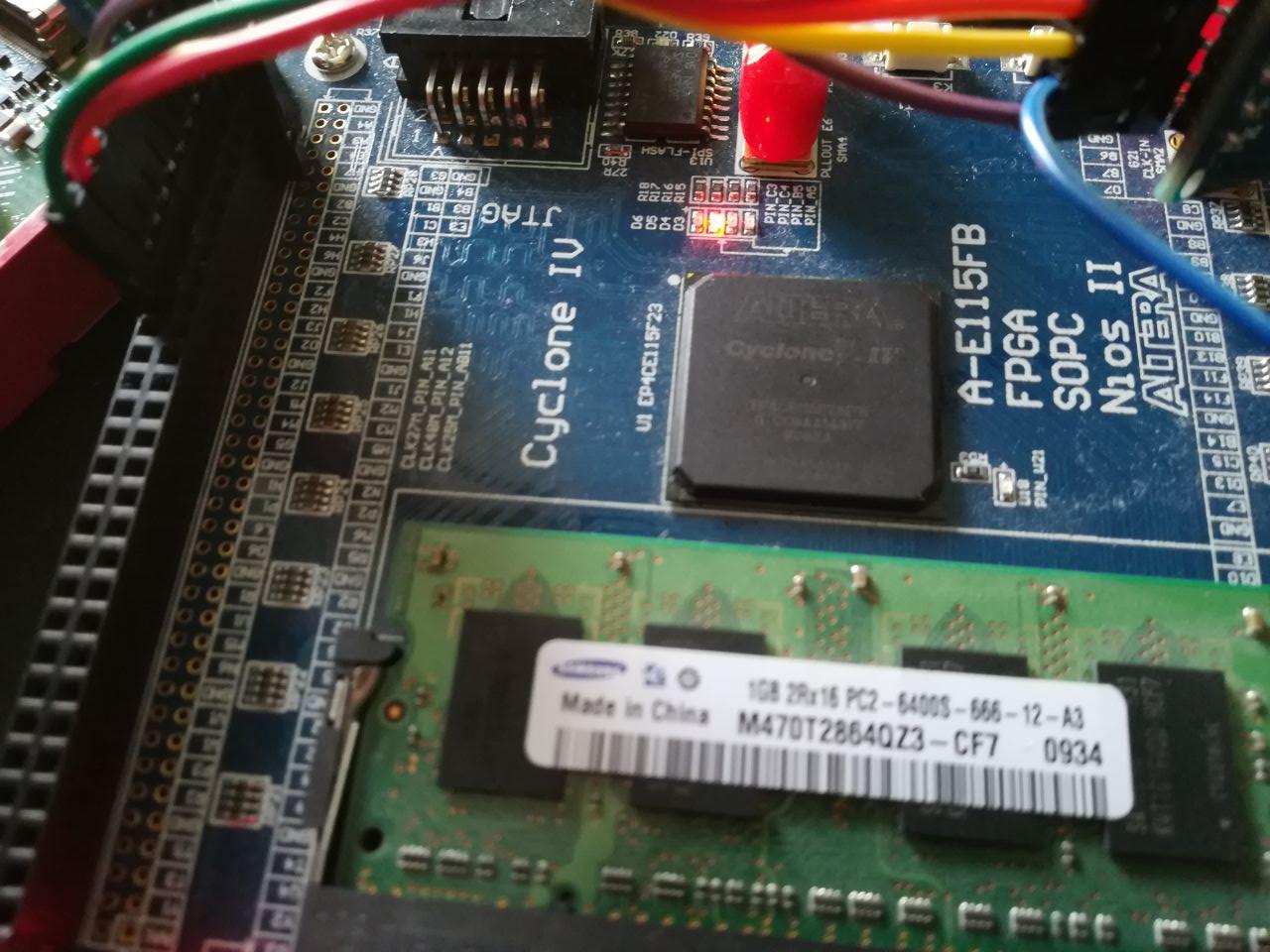

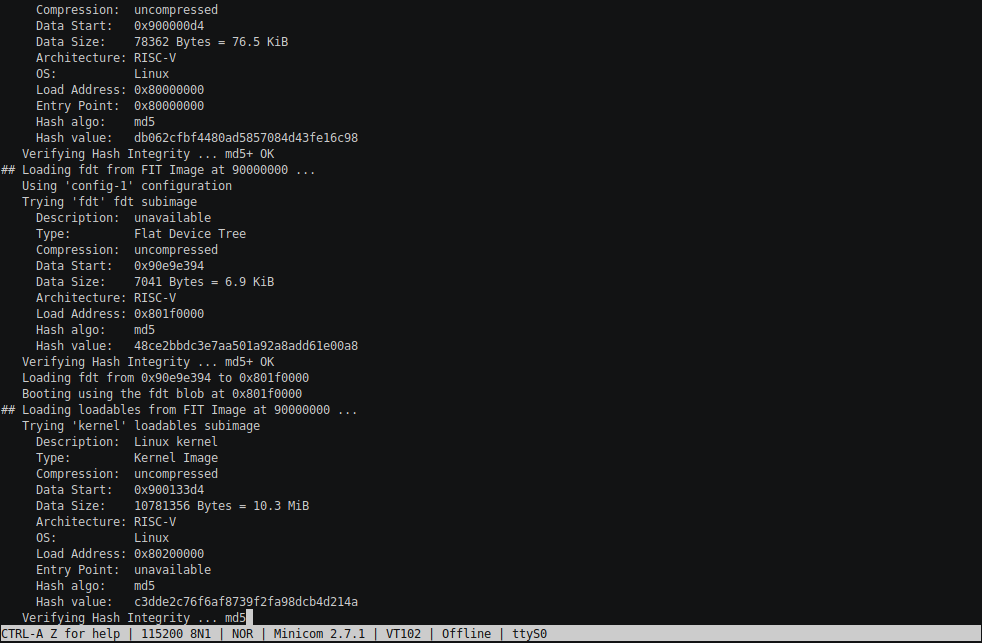

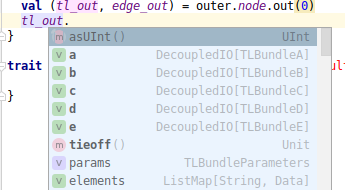

OpenTitan на архитектуре RISC-V — микросхема специального назначения для установки на серверах в дата-центрах и в любом другом оборудовании, где нужно обеспечить аутентичность загрузки, защитить прошивку от изменений и исключить вероятность руткитов: это материнские платы, сетевые карты, маршрутизаторы, устройства IoT, мобильные гаджеты и др.

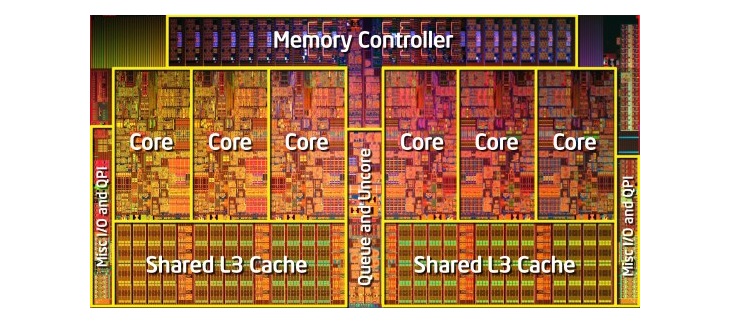

Конечно, подобные модули есть в современных процессорах. Например, аппаратный модуль Intel Boot Guard является корнем доверия в процессорах Intel. Он по цепочке доверия верифицирует подлинность UEFI BIOS перед загрузкой ОС. Но вопрос, насколько мы можем доверять проприетарным корням доверия с учётом того, что у нас нет гарантий отсутствия багов в дизайне, а проверить его нет возможности? См. статью «Доверенная загрузка Шрёдингера. Intel Boot Guard» с описанием того, «как годами клонируемая ошибка на производстве нескольких вендоров позволяет потенциальному злоумышленнику использовать эту технологию для создания в системе неудаляемого (даже программатором) скрытого руткита».

Читать полностью »