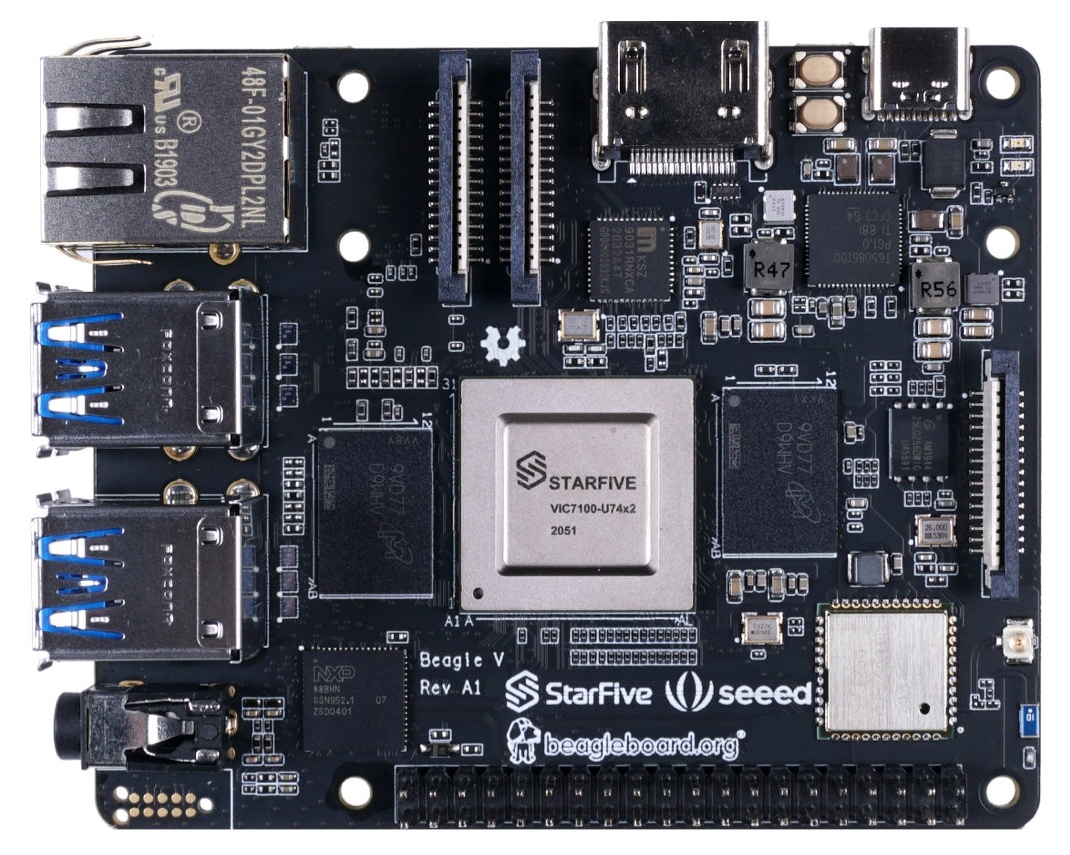

Месяц назад мы публиковали на Хабре статью о том, что китайцам удалось добавить поддержку архитектуры RISC-V в Android. А еще раньше рассказывали о том, что в Поднебесной уже создан процессор, а на его основе — первый ноутбук, который работает на процессоре с архитектурой RISC-V.

Интерес Китая к этой архитектуре объясняется просто — RISC-V позволяет компаниям из Поднебесной обходить санкции США, поскольку архитектура открытая и бесплатная. Сейчас Китай делает дальнейшие шаги в отношении развития технологии — ее поддерживают уже не только коммерческие компании, но и правительство страны. О перспективах этой консолидации, если так можно выразиться — под катом.

Читать полностью »