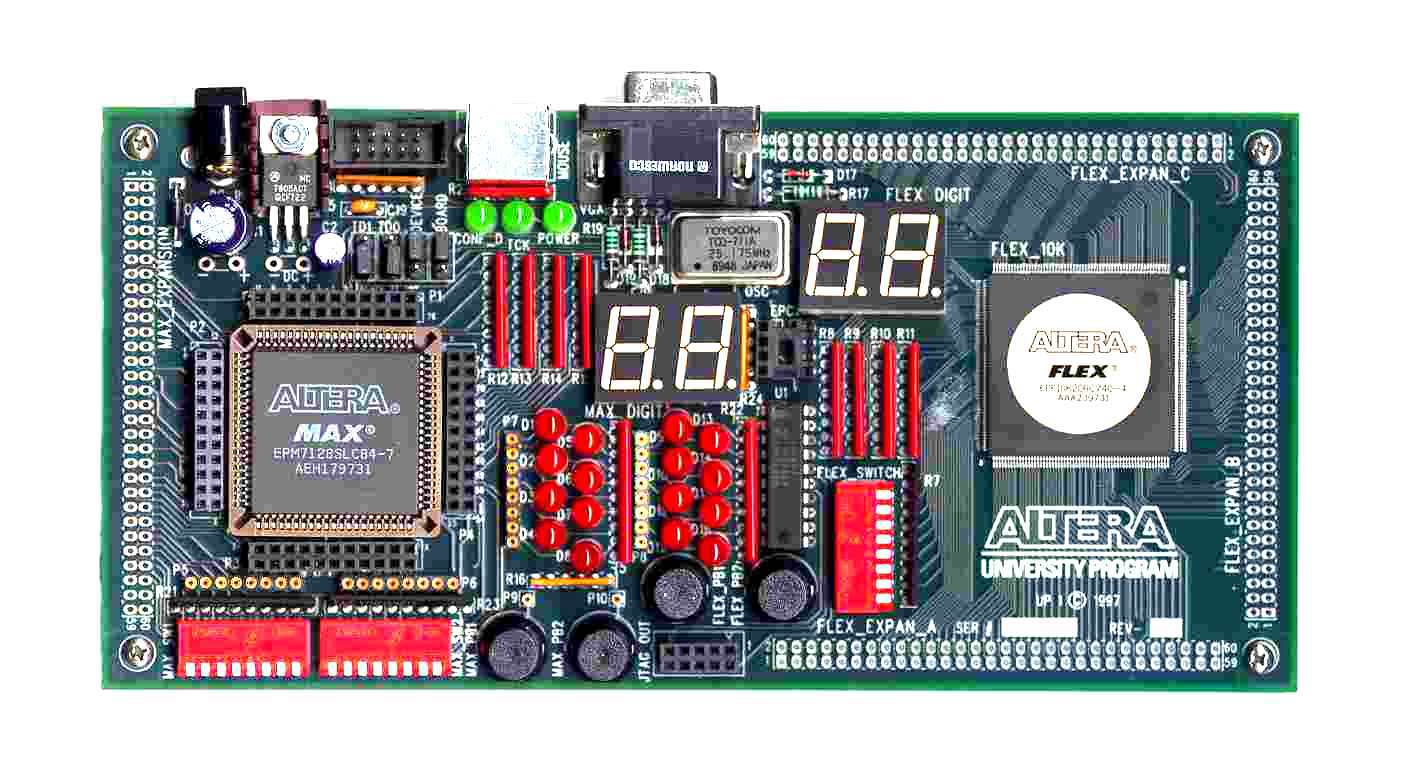

Ректрокомпьютинг бывает разный. Кто-то собирает килограммы древних процессоров, кто-то восстанавливает советские ЕС ЭВМ, кто-то до сих пор разгоняет Celeron в жидком азоте, а мы же насладимся платой Altera University Programm Board UP1 1997 года c древней CPLD MAX7128S и даже поморгаем светодиодом (и не только).

Читать полностью »

Рубрика «Quartus II»

CPLD-ретрокомпьютинг. Часть 1 — Доска для студента

2015-08-11 в 21:16, admin, рубрики: Altera, cpld, fpga, Quartus II, USB Blaster, ретрокомпьютинг, старое железо, метки: CPLDВременной анализ FPGA или как я осваивала Timequest

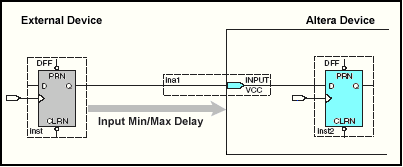

2014-08-07 в 12:50, admin, рубрики: Altera, fpga, Quartus II, timequest, ПЛИС, Программинг микроконтроллеровДоброго времени суток, уважаемые читатели.

На самом деле я инженер-радиофизик и программирование ПЛИС не является моей непосредственной деятельностью, но в один момент понадобилось написать программу для синхронизации нескольких осцилографических модулей. Пришлось осваивать эту науку. О том, какие у меня возникли с этим проблемы, под катом.

Решение проблем связанных с правилами наименования в Quartus II при использовании Schematic

2013-06-21 в 8:11, admin, рубрики: Altera, Quartus II, Железо, Программинг микроконтроллеров, Электроника для начинающих, метки: Altera, Quartus IIЗдравствуйте, Хабросообщество.

Хотел бы поделиться с Вами решением одной проблемы, с которой столкнулся и которую решал довольно долго. Причем помочь решить эту проблему не смогли куча различных радиоэлектронщиков (к которым я обращался за помощью и консультацией), а также 2 отечественных и 1 иностранный форумы по радиоэлектронике.

Я хочу сделать так, чтобы тот, кто это прочитает, никогда не «встал на грабли», на которые я встал и с которыми долго мучался.

Проблема была в том, что я не мог использовать более 1 пина на одном IDC разъеме. Т.е. если мне надо было вывести с устройства 5 бит на 5 пинов, то мне приходилось использовать 5 сорока-пиновых IDC разъемов, используя на каждом лишь 1 пин из 40 имеющихся.

Если на разъеме использовалось более 1 пина (2 и более) — то при проверке осциллографом разъем молчал.

Я очень долго делал все, что мне говорили на форумах — но проблема не решалась. Как выяснилось теперь — проблема заключалась в правилах наименования в Quartus II при использовании Schematic.

Всем тем, кому это будет полезно или интересно — прошу под кат.

Читать полностью »

Исследование процессора и его функциональная симуляция

2013-02-01 в 23:16, admin, рубрики: Altera, Quartus II, testbench, Verilog, Железо, ПЛИС, Процессоры, Электроника для начинающих, метки: Altera, Quartus II, testbench, Verilog, АРМ, ПЛИС

Наверное каждый программист ASM / C / C++ когда-то задумывался о написании своей собственной операционной системы.

И наверное каждый разработчик Verilog / VHDL для ПЛИС когда нибудь задумывался о создании своего процессора.

Собственно реализовать более-менее традиционный процессор на сегодняшний день кажется не очень и большая проблема. Принципы работы процессоров описаны во многих книгах и статьях. Кроме того, существует много процессоров с открытой архитектурой вроде openRISC или openSPARC и многие другие. Их вполне можно рассмотреть перед тем как изобретать свой велосипед.

Я решил поизучать ARM совместимый процессор AMBER. Его исходники есть на http://opencores.org.Читать полностью »