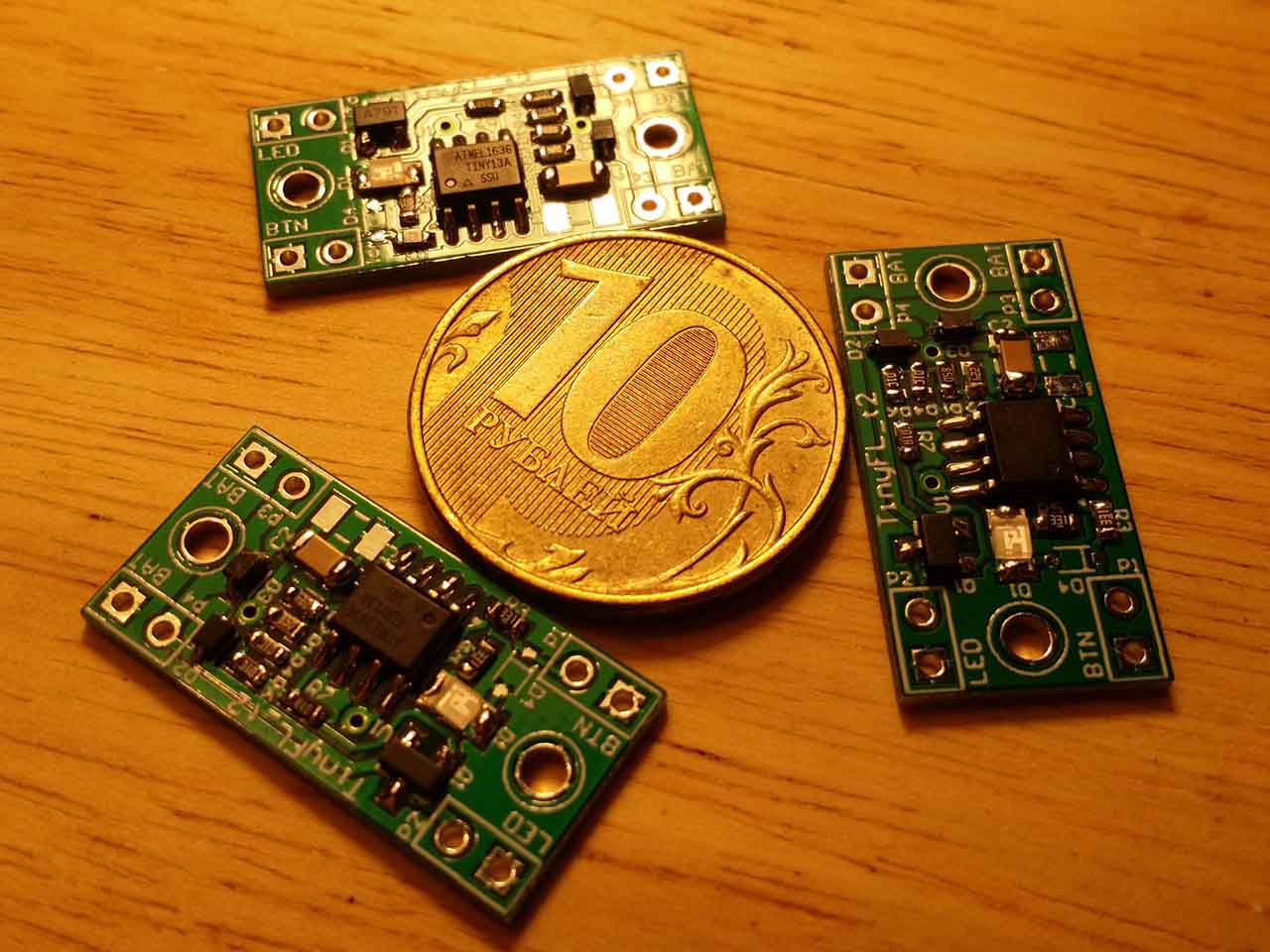

Слава программируемым микроконтроллерам! Их массовость и дешевизна породили целый вал «умной» электроники — и крупные бренды, и стартапы бросились цифровизировать всё, что раньше было аналоговым или вообще не было электроникой. Иной раз посмотришь на робота-пылесоса или какой-нибудь фитнес-браслет, и задаешься мыслью, а что же за электроника там спрятана? Может, какие-нибудь редкие специализированные чипы производства никому не известной китайской компании?

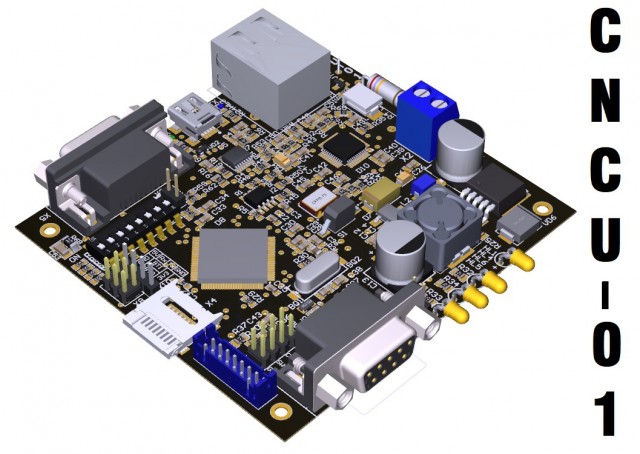

Вы удивитесь, но, даже вскрыв чайник с Wi-Fi, вы увидите знакомые бренды на чипах. И Kingston в том числе — мы поставляем память для вообще любых устройств, где используются программируемые микроконтроллеры. Идет ли речь о смартфоне, терминале в магазине, роботе-пылесосе, да хоть ортопедической кровати, Kingston можно встретить везде. Если вкратце, то смотрите ролик. Если, как и полагается на Хабре, подробно — читайте пост!