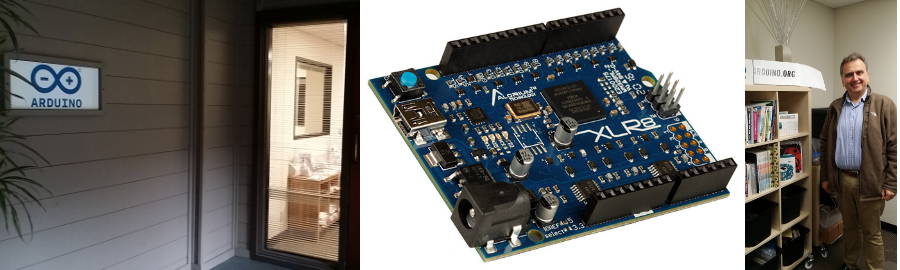

Сегодня утром я заходил в офис калифорнийского отделения Ардуино. Там было межкомпанейское совещание по образовательным программам, на которое меня пригласил менеджер из AMD Тимур Палташев. В конце мероприятия возникла любопытная дискуссия:

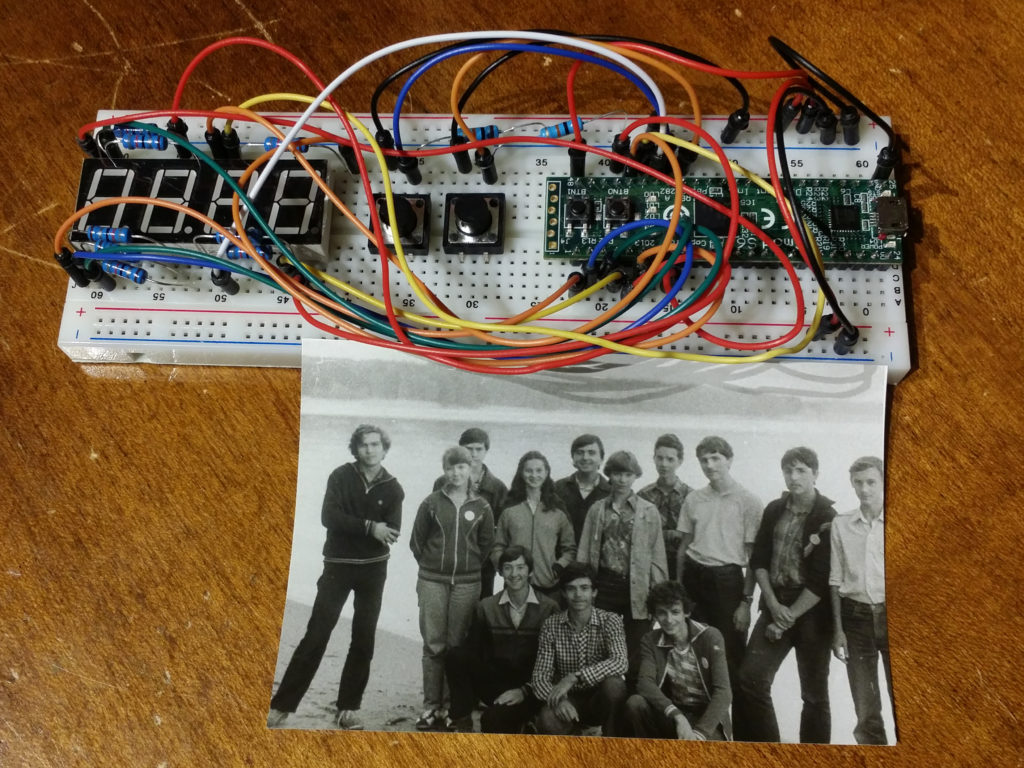

Вот сейчас школьников учат программировать Ардуино и другие устройства на основе микроконтроллеров и встроенных процессоров (Лего, Расберри Пай итд). А вот в 1970-е годы школьников учили здесь же, в Калифорнии, собирать схемы на макетной плате, на транзисторах и микросхемах малой степени интеграции (7400 TTL, CMOS 4000 итд) с элементами И-ИЛИ-НЕ и D-триггерами. Это как бы и прогресс — на микроконтроллере можно написать программу, которая бы осмысленно двигала роботической рукой, чего трудно сделать на индивидуальных логических элементах, но как мы вырастим школьников, которые бы умели проектировать (не программировать) сами микроконтроллеры?

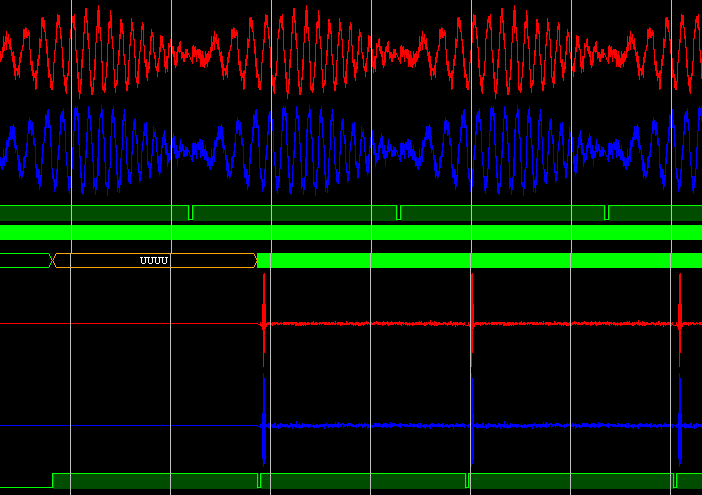

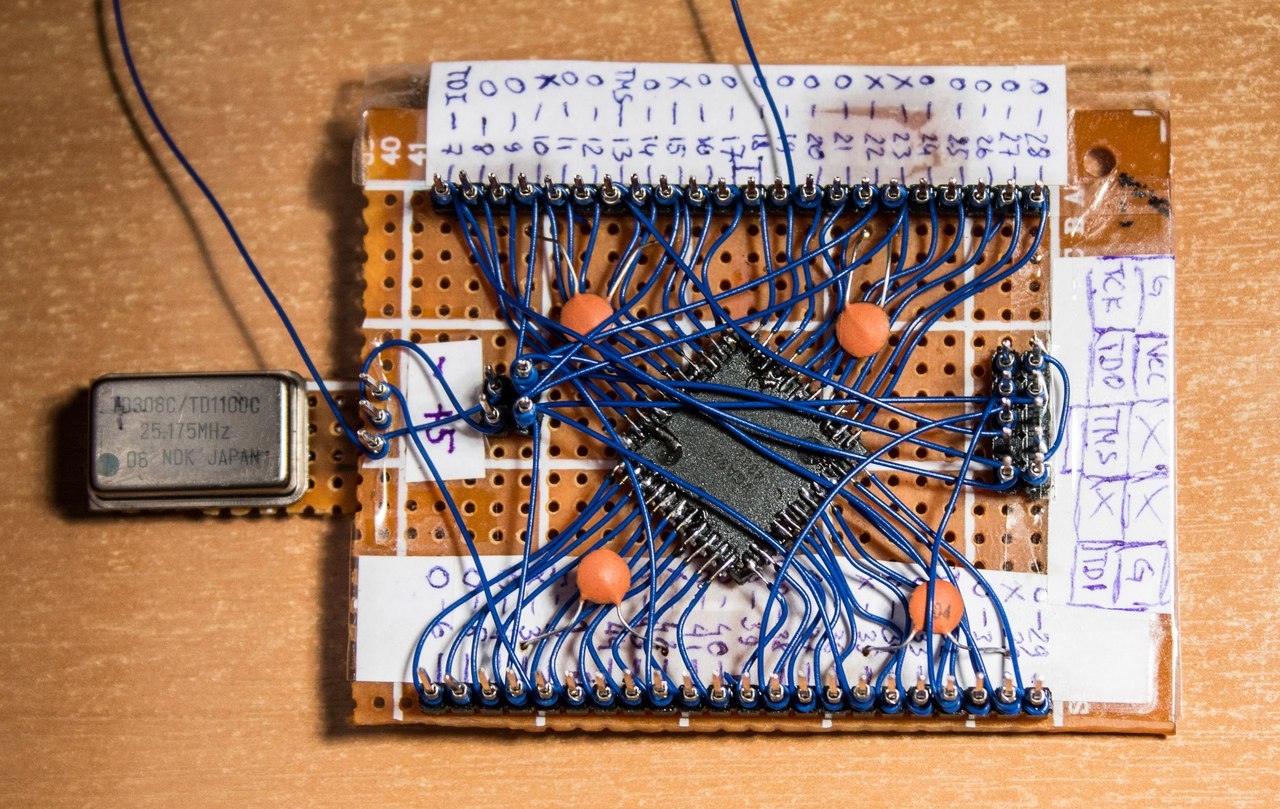

Ответ в общем-то очевиден: между индивидуальными логическими элементами и выпущенными на фабрике микроконтроллерами можно поместить программируемые логические интегральные схемы (ПЛИС / FPGA) и использовать триаду «индивидуальные элементы — ПЛИС-ы — микроконтроллеры» чтобы сформировать у детей более полную картину мира, в которой есть не только софтвер и немножко интерфейсинга, но системное мышление, в которой задачи распределяются между программированием и схемотехникой, и, пусть на очень простом уровне средней школы, понятны все уровни технологии — от физики полупроводников до транзисторов до логических элементов — до уровня регистровых передач — до уровня микроархитектуры/блочного устройства процессора — до уровня архитектуры/системы команд — до уровня программирования на Си и Питоне — до роботов итд.

Идея учить школьников по всему фронту цифровой схемотехники и встроенного программирования звучит хорошо теоретически, но как воплотить это в жизнь?

Читать полностью »