Сезон 1. Проект на Virtex5 не работает, хотя на другой партии кристаллов все в порядке.

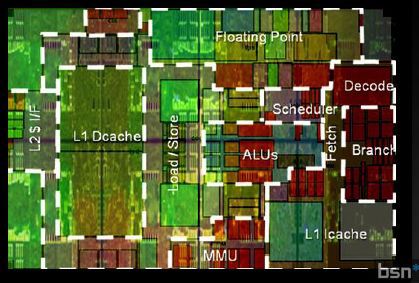

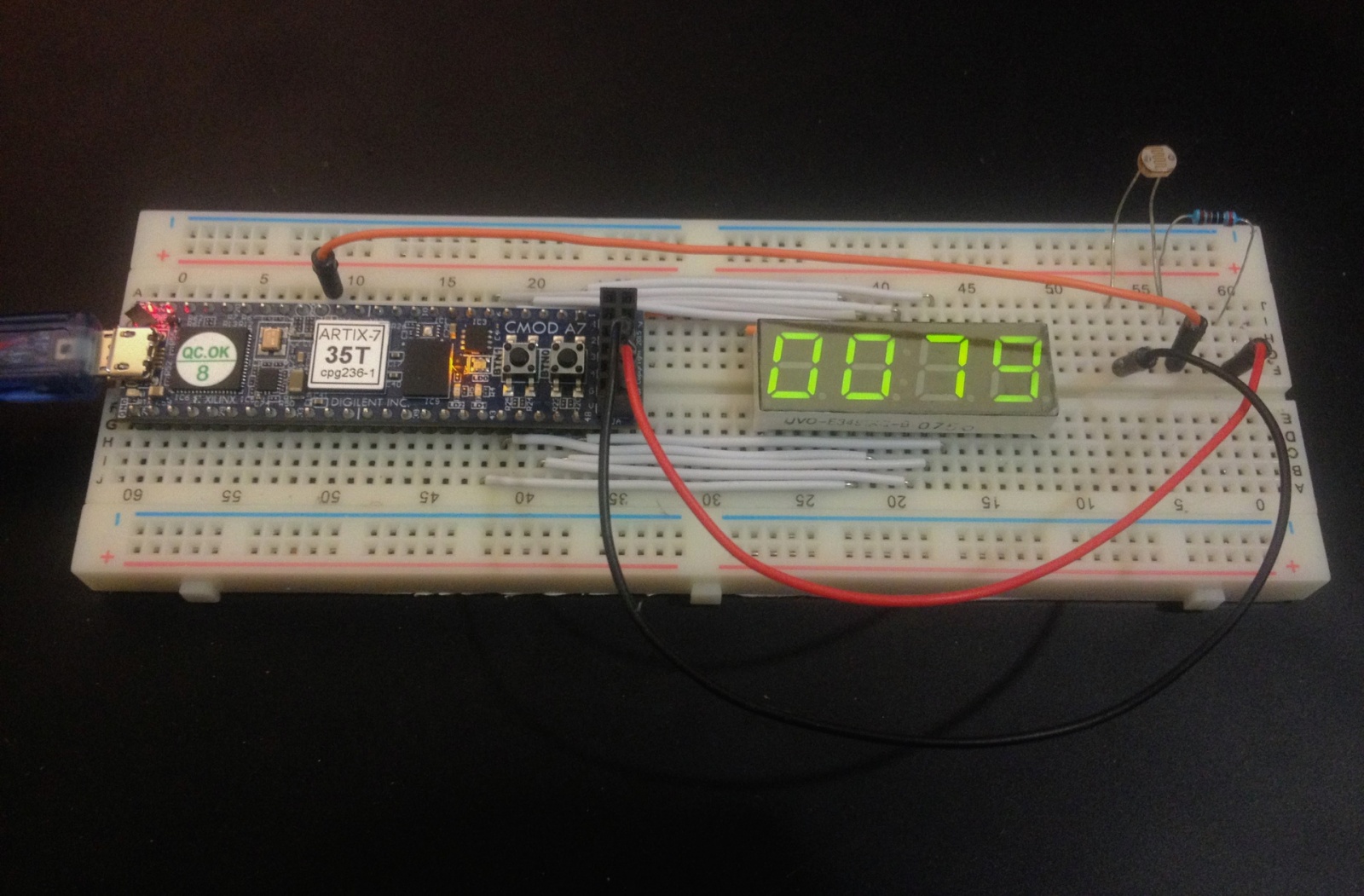

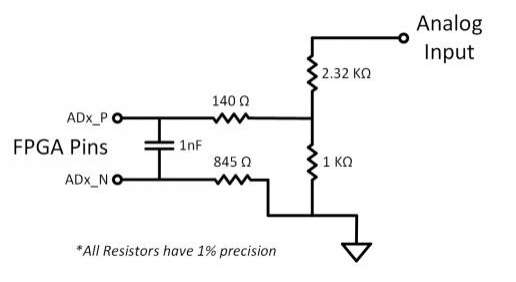

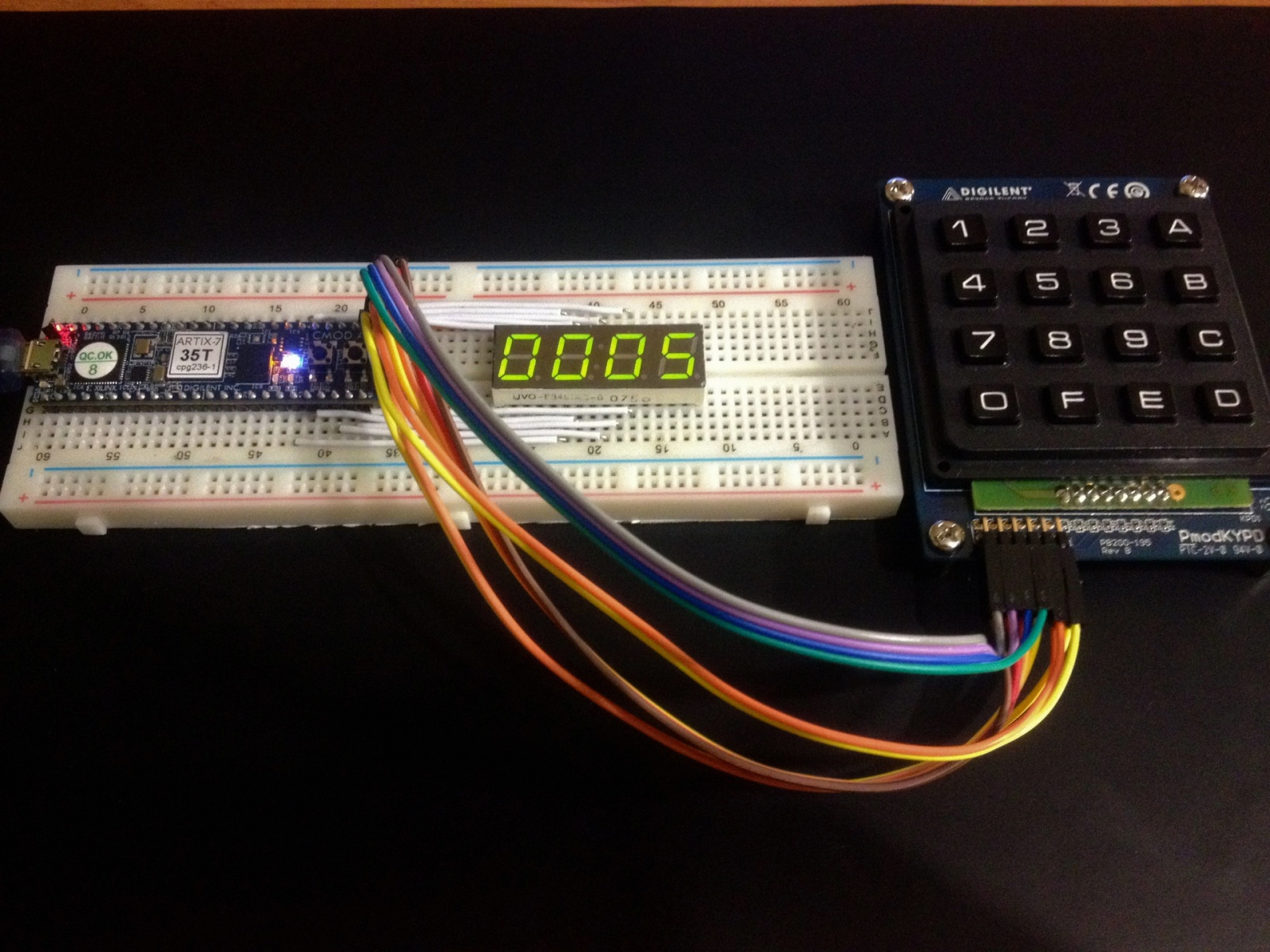

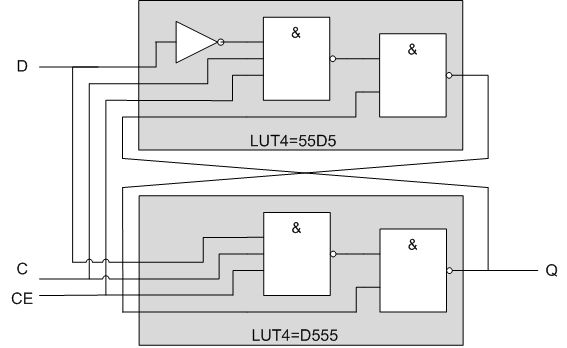

Однажды случилось так, что плата с кристаллом XC5VSX95T не заработала. Было известно, что это новая партия кристаллов. Для проверки проблемы был написан тест, тестирующий подряд все слайсы FPGA. Тестирование кристаллов показало наличие неисправных модулей LUT, входящих по 4 элемента в состав одного слайса. Оказалось, что триггеры в этих слайсах в порядке, и тогда был создан блок памяти на триггерах, которые в свою очередь созданы на LUT. См. рис. 1. Здесь показан пример триггера на LUT4. Каждая ячейка(бит) в тесте отвечает за один слайс. Триггерная ячейка задействует все четыре LUT слайса. Кристалл был разбит на 5 областей (и в другом тесте 9 областей), которые тестировались отдельно, каждый своей прошивкой. Правильное размещение используемых слайсов регламентировалось атрибутами LOC. Неисправность характеризуется невозможностью изменить состояние тестируемого триггера. Выход такого триггера может читаться 0 или 1, но всегда одинаково. Поэтому сначала память заполнялась 1, и проверялась, потом 0, и проверялась. Полный диапазон слайсов такой: X0Y0 – X91Y159. (14720 слайсов)

Рис.1

Читать полностью »