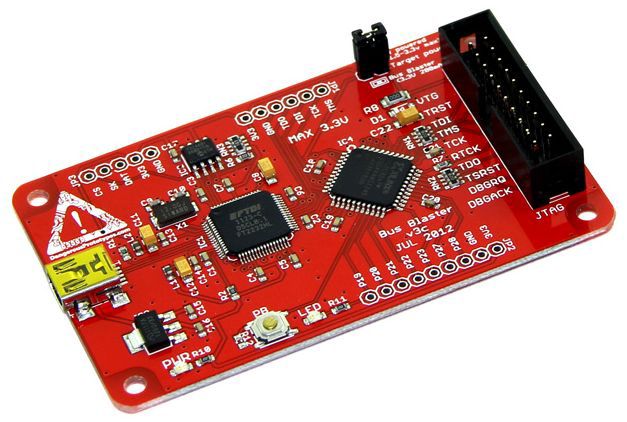

Мне давно хотелось иметь какой-нибудь простой и универсальный аппаратный интерфейс с несколькими входными и выходными сигналами, функциональность которого определяется исключительно софтом, вроде достопамятного программатора PonyProg. И чтобы его можно было использовать не только как чтения/записи прошивок, но и для отладки программ через JTAG. При этом покупать что-либо промышленное, при моем нерегулярном баловстве с электроникой, избыточно и нерентабельно — требовалось что-то из серии «полуфабрикатов», на основе bit-bang.

Что такое bit bang и зачем он нужен

Кое-кто еще помнит, что в счастливые времена Windows 9x каждая системная плата и каждый ноутбук в обязательном порядке имели последовательный (COM) и параллельный (LPT) порты. В ту пору для организации интерфейса с микросхемой ППЗУ, служебными контактами мобильника или передней панели магнитолы достаточно было припаять к разъему порта несколько резисторов, диодов и транзисторов. Все остальное делали обычные пользовательские приложения, самостоятельно формировавшие сигналы нужного протокола путем выставления нулей или единиц на нужных выводах, и считывания сигналов на входах. У клятых буржуев это называлось bit-bang, а у нас — «дрыгоножество», «ногомашество» и т.п.

С переходом на 2k/XP возникли сложности с прямым доступом к портам ввода/вывода, но они успешно решались костылями вроде giveio. Гораздо сильнее портила жизнь более высокая фоновая активность в NT, из-за которой сложнее было выдержать стабильность передачи и приема.

Как известно, на современных компьютерах, тем более — ноутбуках, с аппаратными портами не густо, ибо большинству пользователей они не нужны. USB-адаптеры для подключения устройств с интерфейсами RS232 и Centronics (в просторечии — COM/LPT) хорошо работают лишь в рамках основного назначения, а делать на них «дрыгоножество» проблематично по целому ряду причин. Во-первых, большинство этих адаптеров умеет обрабатывать с хорошей скоростью только сигналы данных (те же Tx/Rx), а управляющие сигналы обрабатывает с большими задержками. Во-вторых, адаптеры различных производителей аппаратно несовместимы, а возможности нестандартного управления через драйвер производителя сильно ограничены. В-третьих, для передачи команд адаптеру почти все драйверы используют отдельные USB-пакеты, что ограничивает частоту смены состояний всего тысячей раз в секунду, чего для многих применений катастрофически мало.

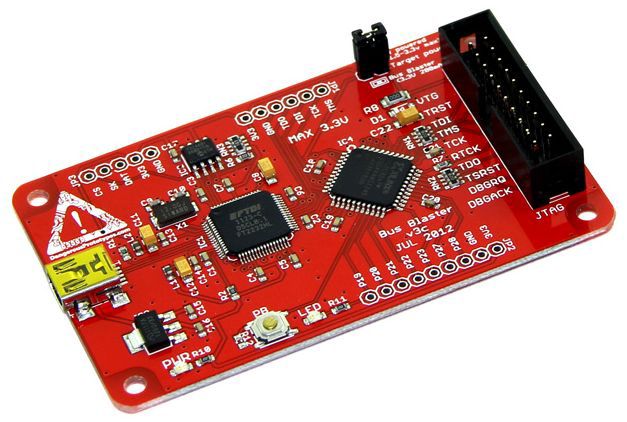

К счастью, компания FTDI уже давно предлагает ряд решений для USB, ориентированных именно на скоростной обмен произвольными сигналами. Беглое изучение вопроса показало, что наиболее популярны в этом плане интерфейсы на микросхемах FT232H/FT2232H.

Читать полностью »