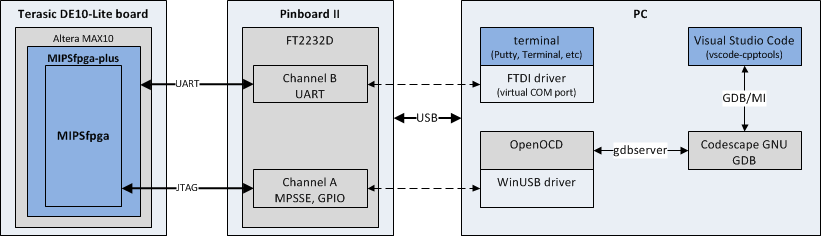

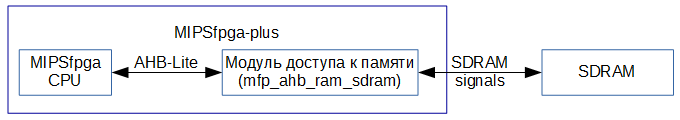

На этой неделе я закончил работу по добавлению поддержки SDRAM в проект MIPSfpga-plus. Теперь при работе с MIPSFpga помимо блочной памяти, ограниченной ресурсами ПЛИС, доступно еще и внешнее ОЗУ.

Данная статья состоит из 2 частей:

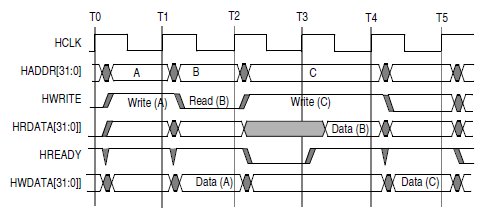

Часть 1. Краткое описание модуля доступа к SDRAM. Пример использования.

Часть 2. Подробное описание работы с памятью, достаточное для того, чтобы в работе модуля смог разобраться человек, ранее не имевший дела с микросхемами ОЗУ. Список литературы.

Предполагается, что читатель как минимум:

- знаком с предметной областью в объеме учебника Харрис-энд-Харрис [1];

- имеет опыт программирования на C, ассемблере, использования gcc;

- имеет минимальный опыт работы с MIPSfpga. Не имея такого опыта, будет логичным начать с более простых вещей, и лишь затем думать о том, как использовать ОЗУ в своей системе.

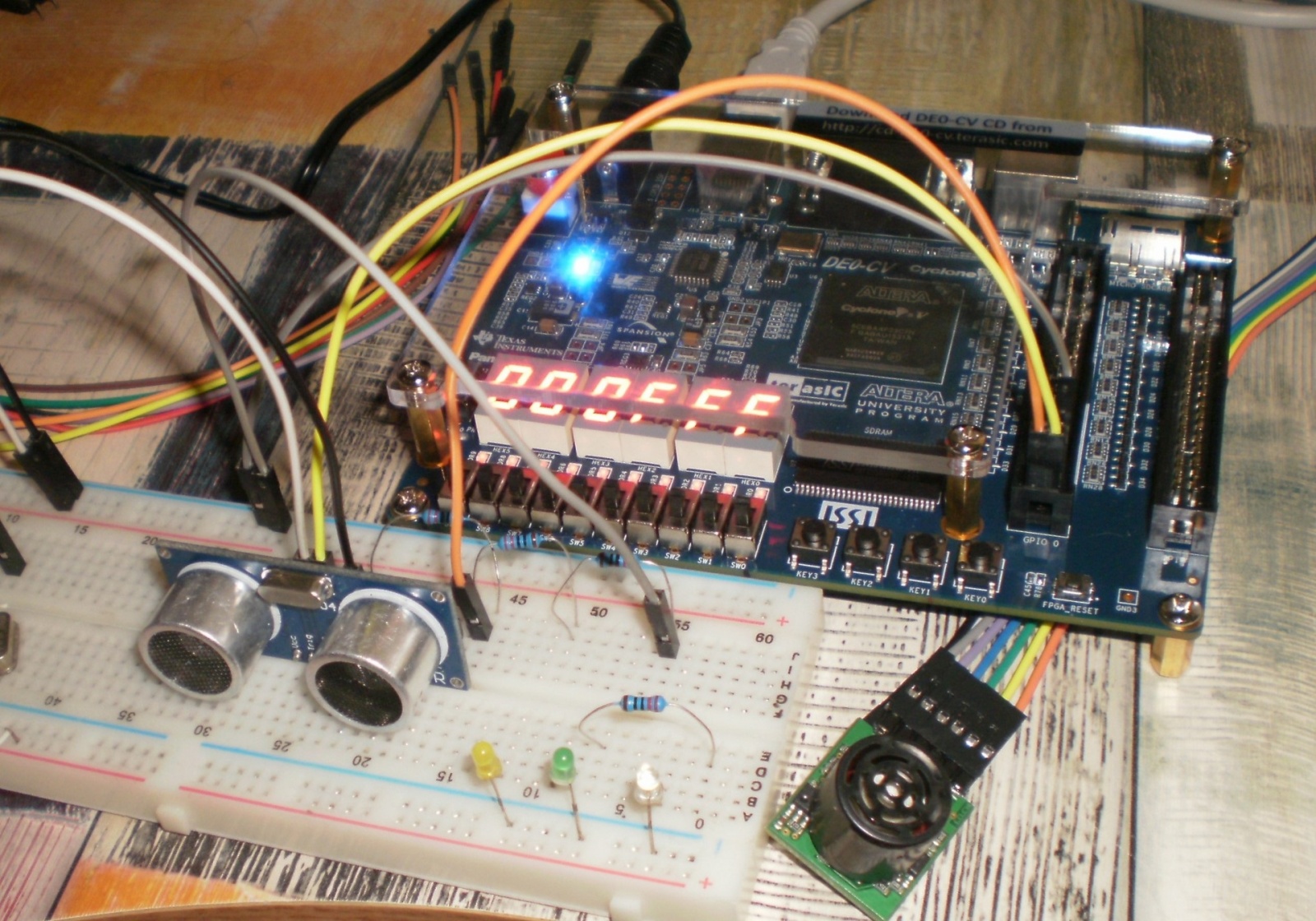

Если вы уже опытный разработчик, то Часть 1 стоит пробежать глазами по диагонали, Часть 2 — не содержит для вас ничего нового. При этом вы можете принести несомненную пользу обществу, если добавите поддержку SDRAM для еще одной отладочной платы. На текущий момент она реализована только для Terasic DE10-Lite — одной из 9 плат, на которые в рамках проекта MIPSfpga-plus было портировано ядро MIPSfpga.

Читать полностью »