Два года назад я начал работать разработчиком ПО. Иногда я рассказывал своим коллегам о студенческом проекте, которым занимался на третьем курсе университета, и они восприняли его настолько хорошо, что я решил написать этот пост1.

Позвольте задать вам вопрос: вы когда-нибудь проектировали собственную архитектуру набора команд (ISA), создавали на FPGA процессор на основе этой ISA и собирали для него компилятор? Запускали ли вы операционную систему на этом процессоре?

А у нас это получилось.

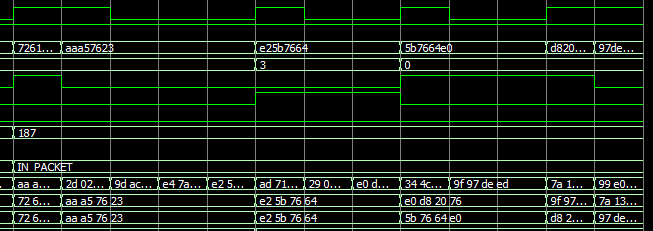

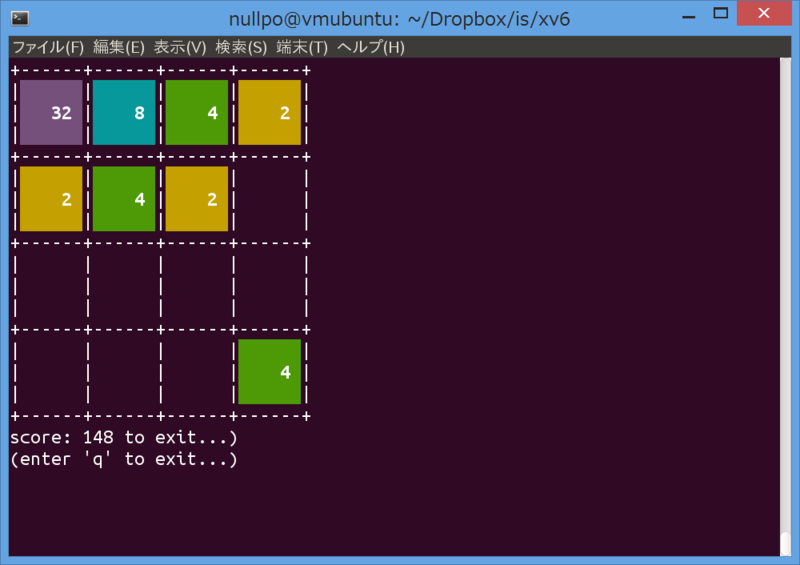

В этом посте я расскажу о своей учёбе в 2015 году, о четырёх месяцах создания самодельного CPU на самодельной архитектуре набора команд RISC, создании самодельного тулчейна C и портировании на этот процессор Unix-подобной ОС Xv6.

Процессорный эксперимент в Токийском университете

Всё это делалось в рамках студенческого экспериментального проекта под названием CPU Experiment. Давайте начнём с того, что же такое CPU experiment.

Читать полностью »