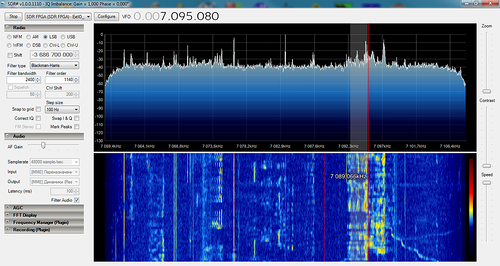

В этой статье я расскажу о том, как на базе отладочной платы DE0-nano сделать достаточно простой КВ SDR приёмник.

Пример принимаемых сигналов:

Читать полностью »

Рубрика «fpga» - 38

Простой SDR приёмник на ПЛИС

2013-12-01 в 20:11, admin, рубрики: diy или сделай сам, fpga, SDR, ПЛИС, радиосвязь, Электроника для начинающих, метки: fpga, SDR, ПЛИСКоротенькое сравнение VHDL и Verilog в помощь начинающим знакомство с ПЛИС

2013-11-06 в 7:48, admin, рубрики: fpga, SystemVerilog, Verilog, vhdl, ПЛИС, Электроника для начинающих, метки: fpga, SystemVerilog, Verilog, vhdl, ПЛИС Исторически так сложилось что ПЛИС я начал изучать только на новой работе.

Это были серии ПЛИС фирмы Altera.

Старшие коллеги на перебой рекомендовали как AHDL так и VHDL для программирования этих микросхем.

В итоге я остановился на языке VHDL, поскольку он является языком высокого уровня, в отличии от ADHL.

Хоть и листинг у последнего был куда приятнее.

И я приступил к изучению всех хитростей и ограничений языка VHDL.

В итоге сошелся на мысли что конструкции языка просто ужасны, а ограничения избыточны для проектирования аппаратуры.

Приведу пример листинга из статьи Делаем таймер или первый проект на ПЛИС

Читать полностью »

Описание блоков памяти на языке VHDL

2013-10-16 в 9:53, admin, рубрики: fpga, vhdl, ПЛИС, Электроника для начинающих, метки: fpga, vhdl, ПЛИС В данной статье показаны основные принципы описания модулей ПЗУ и ОЗУ на языке VHDL. Статья ориентирована на начинающих. Ее цель — дать общее понятие об описании модулей памяти на языке VHDL. Примеры и иллюстрации предены для пакета Quartus II v. 9.1. Предполагается, что читатель знает как создавать проект в пакете Quartus II, проводить его компиляцию и симуляцию.

Читать полностью »

Прямая передача данных между ПЛИС Virtex-7 по шине PCI Express

2013-09-13 в 11:08, admin, рубрики: fpga, pcie, высокая производительность, Железо, ПЛИС, метки: fpga, pcie, ПЛИСАннотация

В данной статье рассматривается передача данных по шине PCI Express с одновременным участием нескольких ПЛИС. В компьютерной системе, к PCI Express шине которой подключено несколько (в нашем случае 8) оконечных устройств (PCIe endpoints) ПЛИС запускается одновременно несколько транзакций передачи данных двух типов: А) DMA передача между ОЗУ и ПЛИС (чтение/запись) и Б) прямая передача данных между двумя ПЛИС (запись). Используя соединение PCI Express x4 Gen 2.0 при обращении в память была получена скорость записи 1451 МБ/с (90% от максимальной). Скорость записи данных между ПЛИС была равна 1603 МБ/с (99 % от максимальной) при длине пакетов 128 байт и 1740 МБ/с (99% от максимальной) при длине пакета 256 байт. Латентность передачи данных между ПЛИС зависит от количества промежуточных коммутаторов, и была равна 0,7 мкс для одного коммутатора и 1 мкс для трех. Также показано, что при одновременных передачах через общий канал скорость отдельных передач не уменьшается до тех пор, пока суммарная скорость передачи не превышает пропускную способность общего канала; затем канал используется на 100%, а его пропускная способность делится поровну между устройствами.

Читать полностью »

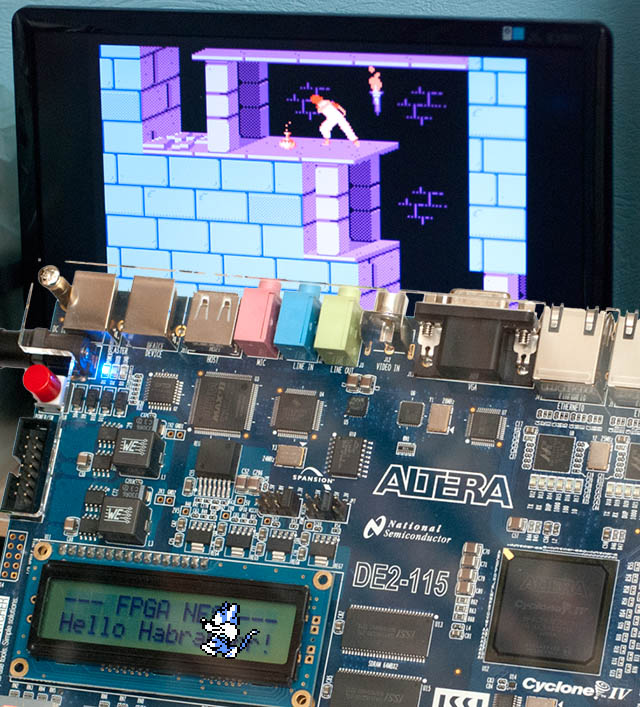

NES, реализация на FPGA

2013-07-08 в 7:58, admin, рубрики: Altera, dendy, diy или сделай сам, fpga, Nes, Verilog, денди, игровая консоль, Игровые приставки, ностальгия, ПЛИС, метки: Altera, dendy, fpga, Nes, Verilog, денди, игровая консоль, ностальгия, ПЛИСДобрый день!

Я хочу рассказать о проекте игровой консоли Nintendo Entertainment System (NES) в реализации на FPGA. На постсоветском пространстве она известна как Dendy.

Желающих посмотреть видео и поностальгировать прошу под кат.

Читать полностью »

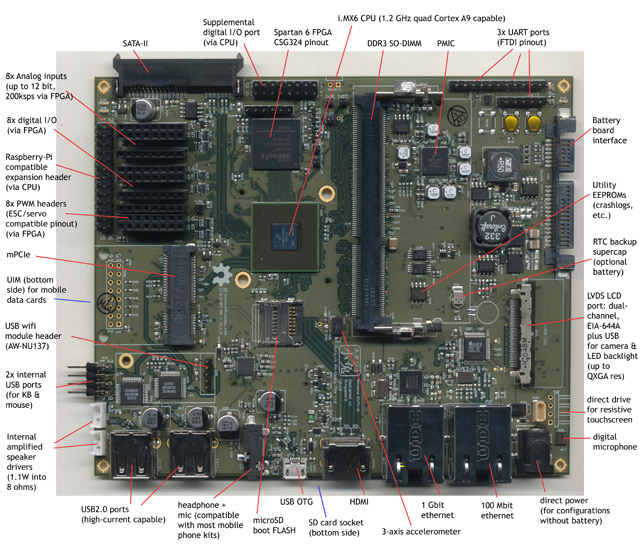

Свободный ноутбук Novena

2013-07-07 в 8:53, admin, рубрики: diy или сделай сам, fpga, Железо, Ноутбуки, метки: fpga, retinaИзвестный хакер, автор книги “Hacking Xbox” Эндрю Хуанг (Andrew “bunnie” Huang) в июне 2012 года вместе с коллегами начал разработку свободного ноутбука Novena на процессоре Freescale iMX6. Идея в том, чтобы у сообщества была открытая платформа, с открытой документацией и руководством по программированию, так что каждый может собрать из комплектующих себе ноутбук/маршрутизатор/etc. на свой вкус, с любой клавиатурой, корпусом и размером экрана.

Читать полностью »

Простой радиопередатчик FM диапазона на основе ПЛИС

2013-05-06 в 23:39, admin, рубрики: diy или сделай сам, fpga, радиосвязь, Электроника для начинающих, метки: fpga 7 мая — День Радио!

Надеюсь эта заметка будет как раз кстати.

Совсем недавно на хабре была статья про проект на базе платы Raspberry Pi — к ней подключался просто кусок провода и… это все. Программа, работающая на Raspberry Pi умудрялась вести вещание в FM диапазоне просто через этот кусок провода.

Вот ссылка на ту статью на хабре.

Теперь уже похожий проект появился и для ПЛИС Altera Cyclone III. Опять короткий кусок провода подключен прямо к выходу микросхемы, в данном случае микросхемы ПЛИС.

Аудио файл в формате WAV 22050Гц, 8 бит, МОНО просто передается в плату через последовательный порт. Плата принимает байты и ведет вещание этого потока в FM диапазоне на частоте 90МГц.

Демонстрационное видео трансляции есть на youtube, правда музыка несколько усыпляющая.

Видно, что мелодия принимается не только бытовым радиоприемником рядом с платой, но и в автомобиле во дворе, примерно в пятнадцати метрах.Читать полностью »

Непоследовательный компьютер

2013-02-15 в 18:23, admin, рубрики: fpga, биоинформатика, Исследования и прогнозы в IT, ненормальное программирование, отказоустойчивость, метки: fpga, отказоустойчивость Двое английских учёных Peter Bentley и Christos Sakellariou создали компьютер, который подобно мозгу человека выполняет инструцкии не последовательно, а сегментами в случайном порядке.

По словам учёных, такой механизм позволяет этому компьютеру адаптироваться к критическим ситуациям и обходить их без остановки работы.

Читать полностью »

Высокочастотный трейдинг (HFT) с использованием FPGA

2012-12-20 в 16:36, admin, рубрики: fast, finance, FIX, fpga, HFT, trading, ultra low-latency, высокая производительность, Программинг микроконтроллеров Данная статья рассказывает о разработке узкоспециализированного аппаратного устройства для целей HFT. Его специализация направлена на достижение минимально возможных временных задержек для обработки рыночных данных и, следовательно, на уменьшение времени раунд-трипа при осуществлении сделок. Реализация, описанная в этой работе, осуществляет разбор пакетов Ethernet, IP и UDP, а также FAST протокола, который является наиболее распространенным при передаче рыночной информации. Для подобных целей был разработан собственный движок микрокода, с поддержкой набора команд и компилятором, благодаря чему достигается поддержка широкого круга применяемых в трейдинге протоколов. Конечная система была реализована в RTL коде и исполняется на FPGA. Данный подход показывает преимущество в 4 раза, по сравнению с полностью программными решениями.

Читать полностью »

VGA адаптер на ПЛИС Altera Cyclone III

2012-11-09 в 0:20, admin, рубрики: Altera, fpga, VGA, ПЛИС, Программинг микроконтроллеров, метки: Altera, fpga, vga, ПЛИС  Привет — в этой статье я собираюсь поделиться своими успехами в освоении ПЛИС Altera Cyclone III. После мигания лампочками и игр со счетчиками — решил сделать что то более серьезное. Сделал я простейший VGA адаптер. Об основных его частях и пойдет речь. Статья больше ориентирована на начинающих, так как для опытных эта задача не составит труда, но для освоения, на мой взгляд — хорошая тренировочная задача. Эксперименты я свои провожу на отладочной плате Altera DE0. Описывать схему я буду на Verilog, Среда — Quartus II v 12.0. Итак — добро пожаловать под кат: Читать полностью »

Привет — в этой статье я собираюсь поделиться своими успехами в освоении ПЛИС Altera Cyclone III. После мигания лампочками и игр со счетчиками — решил сделать что то более серьезное. Сделал я простейший VGA адаптер. Об основных его частях и пойдет речь. Статья больше ориентирована на начинающих, так как для опытных эта задача не составит труда, но для освоения, на мой взгляд — хорошая тренировочная задача. Эксперименты я свои провожу на отладочной плате Altera DE0. Описывать схему я буду на Verilog, Среда — Quartus II v 12.0. Итак — добро пожаловать под кат: Читать полностью »