Ты ждал знак? Вот он!

Много лет я не решался начать программировать ПЛИС, потому что это сложно, дорого и больно (как мне казалось). Но хорошо, когда есть друзья, которые помогают сделать первый шаг. И теперь я не понимаю одного — ПОЧЕМУ Я ЖДАЛ ТАК ДОЛГО?

Сейчас я помогу сделать первый шаг и тебе!

Рубрика «fpga» - 37

Сумбурные размышления о будущем технологии FPGA

2014-09-09 в 8:10, admin, рубрики: fpga, виртуальная память, игра жизнь, ненормальное программирование, параллельное программирование, ПЛИС, Электроника для начинающих

Работая над очередным игровым (обучающим) проектом ПЛИС для платы Марсоход2 я столкнулся с тем, что мне явно не хватает места в кристалле. Кажется и проект не очень сложный, но моя реализация такова, что требует много логики. В принципе, это ерунда, дело-то житейское. Ну, если очень будет нужно, то можно выбрать ПЛИС с большей емкостью. Собственно мой проект — это игра «Жизнь», но реализованная в ПЛИС на языке Verilog HDL.

Про логику игры, рассказывать не буду, про нее и так написано уже достаточно.

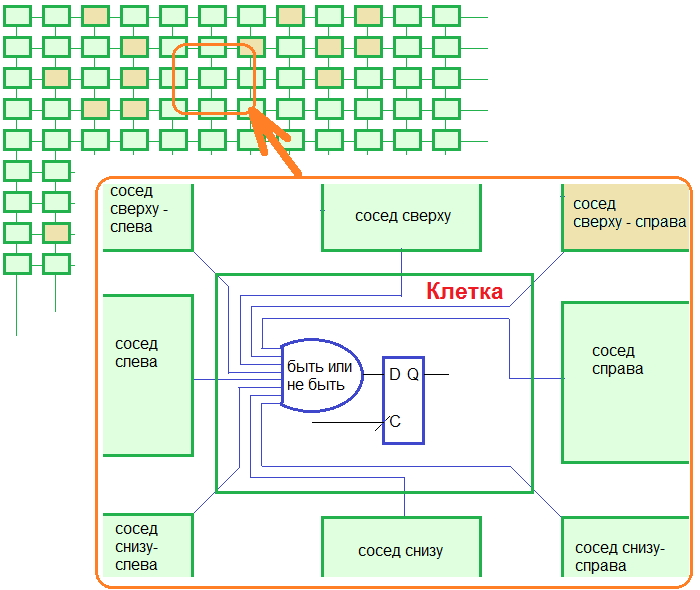

Идея проекта вот такая: каждая клетка в игровом поле представляет собой самостоятельный вычислитель. В каждом вычислителе есть своя логическая функция и свой регистр, который хранит текущее состояние клетки (живая/не живая). Все пространство для жизни клеток — это двумерный массив вычислителей, вычислители образуют целую сеть. Все вычислители работают синхронно, так как на все регистры подается единая тактовая частота. Рисунок вверху должен прояснить схему проекта.

Так вот. На моей плате стоит ПЛИС Cyclone III EP3C10E144C8 компании Альтера. 10тыс логических элементов. Сперва я думал, что смогу сделать двумерный массив клеток 128x64=8192 клетки. Не помещается. 64x64=4096 — то же не помещается в кристалл. Как же так. Я сумел вместить в ПЛИС только 32x16=512 клеток. Пичалька…

Размышления приводят меня к мысли, что возможно, в будущем, технология ПЛИС перерастет в нечто большее, чем программируемая логика. Вот об этом своем видении я хотел бы рассказать. Искушенному читателю сразу скажу, что многое далее написанное есть просто плод воображения и может быть даже бред.

Однако..Читать полностью »

Взгляд на 10G Ethernet со стороны FPGA разработчика

2014-08-24 в 9:47, admin, рубрики: 10g, 10gbe, ethernet, fpga, phy, xaui, xgmii, ПЛИС, Сетевое оборудование, Сетевые технологииВсем привет!

Многие специалисты знают, что топовое сетевое оборудование использует специальные чипы для обработки трафика. Я принимаю участие в разработке таких молотилок и хочу поделиться своим опытом в создании таких высокопроизводительных девайсов (со интерфейсами 10/40/100G Ethernet).

Для создания нового канала сетевики чаще всего берут оптику, пару SFP+ модулей, втыкают их в девайсы: радостно загораются лампочки, пакеты начинают приходить и чип начинает его передавать получателям. Но как чип получает пакет из среды передачи? Если интересно, то добро пожаловать под кат.

Читать полностью »

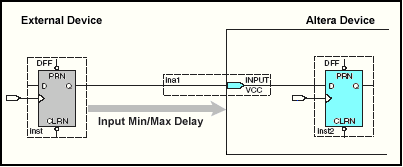

Временной анализ FPGA или как я осваивала Timequest

2014-08-07 в 12:50, admin, рубрики: Altera, fpga, Quartus II, timequest, ПЛИС, Программинг микроконтроллеровДоброго времени суток, уважаемые читатели.

На самом деле я инженер-радиофизик и программирование ПЛИС не является моей непосредственной деятельностью, но в один момент понадобилось написать программу для синхронизации нескольких осцилографических модулей. Пришлось осваивать эту науку. О том, какие у меня возникли с этим проблемы, под катом.

Плис Achronix – опыт освоения

2014-07-24 в 14:18, admin, рубрики: Achronix, fpga, Speedster, Verilog, высокая производительность, Железо, ПЛИС, Программинг микроконтроллеров

За более чем десятилетний срок работы с ПЛИС, мне довелось работать с продукцией четырех разных производителей. При таком разнообразии невольно обращаешь внимание как на общие черты процесса разработки, так и на особенности, присущие той или иной компании. И вот, пару месяцев назад мне неожиданно представилась уникальная возможность близко познакомиться с новым семейством ПЛИС, производимым небольшой, но амбициозной компанией из Калифорнии. Я говорю сейчас о самом молодом производителе ПЛИС – компании Акроникс (Achronix) и выпускаемой ею ПЛИС Speedster22i HD1000.

Читать полностью »

Странное поведение компании STmicroelectronics

2014-07-10 в 13:55, admin, рубрики: DSM, dsp, fpga, stm32, stmicroelectronics, Железо, Программинг микроконтроллеровНаша компания успешно использовала некоторое время чипы серии DSM компании STmicroelectronics — DSM2150F5V. Это микросхема в корпусе TQFP80, которая предназначена для совместной работы вместе с сигнальными процессорами DSP Blackfin компании Analog Devices. Мы эту микросхемку именно так и использовали. В составе DSM2150F5V находятся сразу и FLASH-память для программы, откуда может загрузиться DSP, и программируемая логика, которую можно использовать для каких-то дополнительных функций. Как написано в даташите (который найти в Интернете становится все труднее и труднее, об этом далее), DSM2150F5V специально предназначена для упрощения подключения памяти, внешней логики, потов ввода/вывода к DSP-процессорам Analog Devices семейств ADSP-218x, 219x, 2106x, 2116x, 2153x и TS101. Все в одном, удобная микросхема.

Все было здорово и хорошо, делали мы на микросхеме DSM2150F5V свои приборы и радовались. Но в один не очень прекрасный день к нам пришел снабженец и сообщил, что микросхему DSM2150F5V купить невозможно, никто её больше не продает. Читать полностью »

Intel собирается выпустить серверные процессоры Xeon со встроенной FPGA

2014-06-21 в 8:11, admin, рубрики: fpga, gpgpu, intel xeon, высокая производительность, Железо, Процессоры, метки: fpga, gpgpu, intel xeon

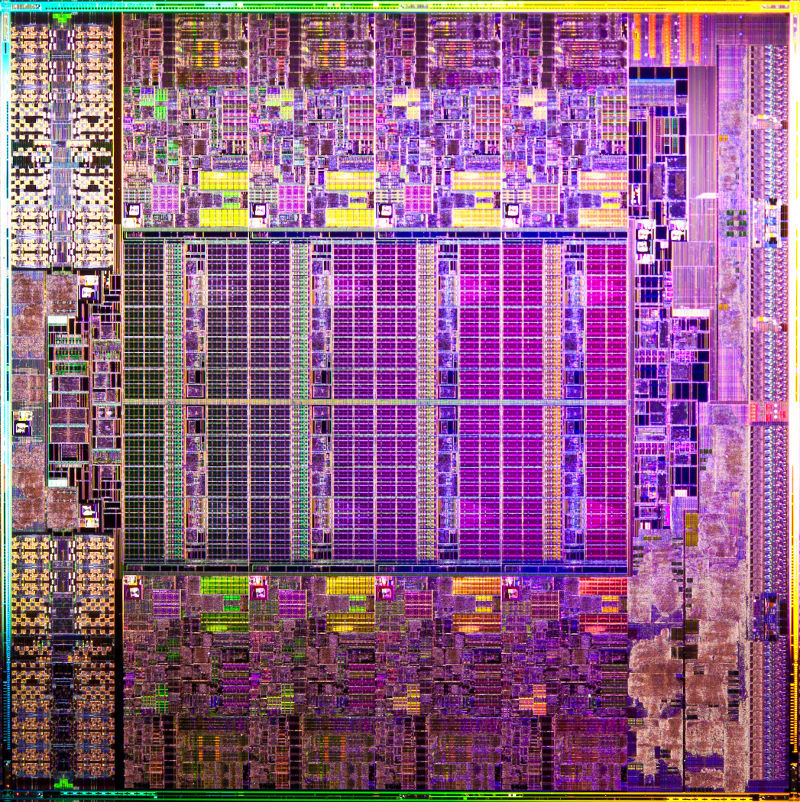

Восьмиядерный процессор Xeon

Корпорация Intel планирует включить в состав своих чипов Xeon программируемую пользователем вентильную матрицу (FPGA). FPGA позволяет пользователю переконфигурировать логику работы интегральной схемы, оптимизировав её под решение конкретной задачи. Это позволяет ускорить некоторые вычисления на порядок, или намного снизить энергопотребление. Другими словами, это позволит каждому пользователю создавать на кристалле Xeon собственный сопроцессор, заточенный под конкретные задачи.

Читать полностью »

Quaternion Encryption Scheme (QES) на FPGA, XeonPhi, GPU

2014-06-19 в 8:17, admin, рубрики: c++, fpga, nvidia tesla, opencl, Алгоритмы, высокая производительность, ПЛИС, сопроцессор, шифрование, метки: fpga, nvidia tesla, opencl, ПЛИС, сопроцессор, шифрование -na-FPGA-XeonPhi-GPU.jpg)

Привет!

Шифрование данных с помощью кватернионов выполнялось на FPGA DE5-NET, XeonPhi 7120P, GPU Tesla k20.

У всех троих приблизительно одинаковая пиковая производительность, но имеется разница в энергопотреблении.

Дабы не нагромождать статью лишней информацией предлагаю вам ознакомиться с краткой информацией о том что такое кватернион и матрица поворота в соответствующих статьях википедии.

Каким же образом можно зашифровать и расшифровать данные с помощью кватернионов? Довольно просто!

Для начала возьмем кватернион: q = w + x*i + y*j + z*k и составим на его основе матрицу поворота, которую назовем, например P(q).

Прим. картинка ниже из википедии и матрица там названа Q.

Microsoft переходит на процессоры собственной разработки

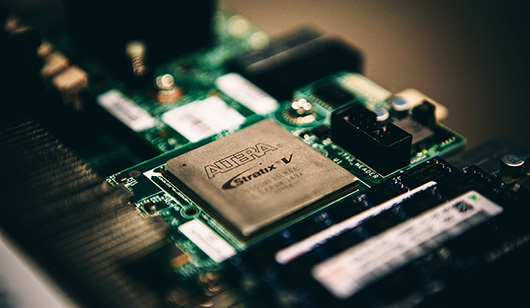

2014-06-18 в 12:12, admin, рубрики: Bing, fpga, microsoft, xeon, высокая производительность, Процессоры, метки: Bing, fpga, microsoft, xeon Союз между компаниями Microsoft и Intel всегда задавал стандарты для всей компьютерной индустрии, однако времена потихоньку начинают меняться. В Microsoft не очень довольны темпами развития современных серверных процессоров, и потому решили начать экспериментировать с чипами FPGA, в целях добиться более высокой производительности в обслуживании своей поисковой системы Bing.

Производителем FPGA чипов выступает компания Altera, пионер в области программируемых чипов. В пилотном тестировании было задействовано 1632 сервера, каждый из которых был оснащён классическим x86-процессором Intel Xeon и платой с чипом FPGA. Платы были объединены в единую машинную поисковую сеть под названием Catapult, через которую шли запросы с сайта Bing в обход процессоров Xeon.

Читать полностью »

-na-FPGA-XeonPhi-GPU-2.png)