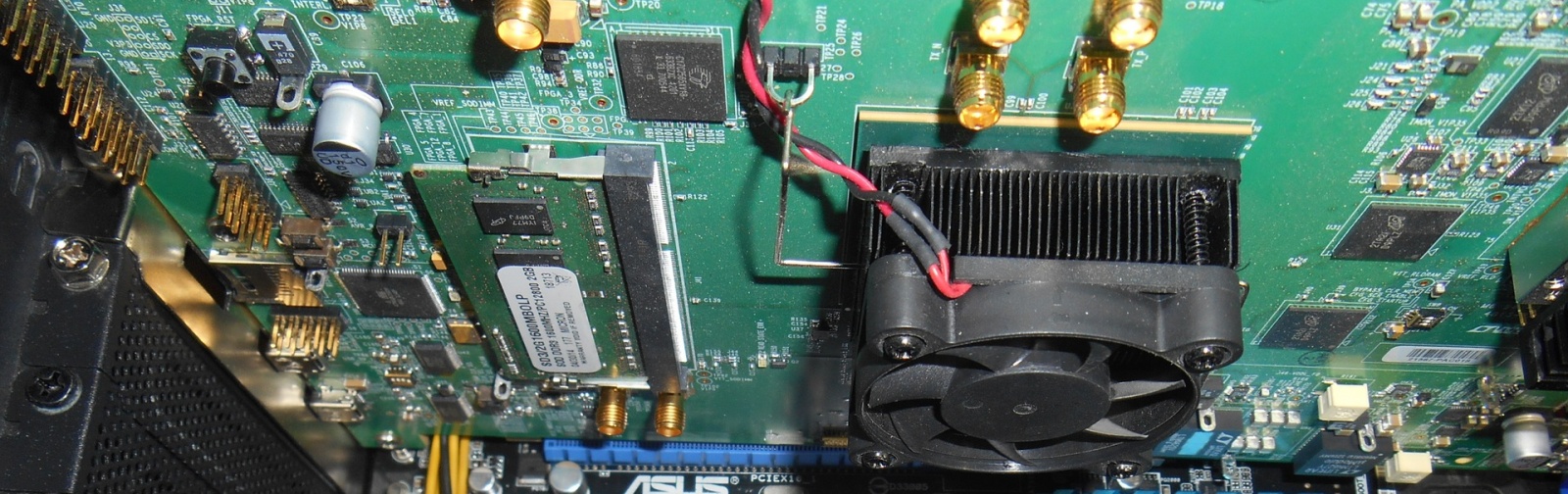

В 22-м выпуске подкаста мы разговаривали об аппаратной базе современных маршрутизаторов и коммутаторов — ASIC и FPGA, передача данных в пределах платы, его обработка, программирование FPGA.

В тот раз мы не затронули фабрики коммутации, которые обеспечивают, как передачу данных между линейными платами, так и между сетевыми процессорами одной платы. Случаются в нашей жизни ситуации, когда именно фабрики коммутации становятся узким местом и возникает понятие Back Pressure.

В 23-м выпуске Александр Клиппер рассказывает о маршрутизаторе Compass-EOS, в котором полностью отказались от фабрик коммутации в пользу так называемых D-Chip — эксклюзивная разработка компании Compass-EOS. Теперь все чипы и платы могут общаться друг с другом напрямую. Это становится возможным, поскольку чипы взаимодействуют в оптической среде, показатели которых значительно выше, чем у медного проводника.

Но лучше, чем инженер вендора я об этом не расскажу.

Кроме того, Дмитрий Булыгин представляет вторую часть Истории Связи. От открытия удивительных свойств электричества переходим к первым телеграфам. А ещё про то, как Морзе придумал свою азбуку и внедрил её в телеграф, про первые факсы и роль русских учёных.

Подписаться на podfm. Добавить RSS в подкаст-плеер.

Скачать все выпуски подкаста вы можете с помощью BT Sync (код: BYENRHD5UNKD5ZDIYFSB63WG2PEY2GIUN) или с яндекс-диска.

Читать полностью »

Рад сообщить, что реверс-инжениринг КР580ВМ80А полностью завершен. Получена полная принципиальная схема и Verilog-модель. В невероятно короткие сроки схему восстановил Vslav (1801ВМ1@gmail.com).

Рад сообщить, что реверс-инжениринг КР580ВМ80А полностью завершен. Получена полная принципиальная схема и Verilog-модель. В невероятно короткие сроки схему восстановил Vslav (1801ВМ1@gmail.com).