Разрабатываю систему (аппаратно-программный комплекс) имитации мышления (сокращённо СИМ). Как задачу минимум решил сконцентрироваться на собеседнике для одиноких людей, преимущественно престарелых и инвалидов. В перспективе планирую использовать наработки проекта для создания контролируемого искусственного разума (КИР).

Что у меня есть для реализации идеи?

1. Создана с нуля логическая база, равная по возможностям «нечёткой логики», но почти такая простая, как бинарная. Практически это тритичная логика (больше, меньше или равно) с четвёртым значением, которое можно, в зависимости от контекста интерпретировать как «неизвестно» или «безразлично». Для расширения значений, при необходимости, используются целочисленные коэффициенты.

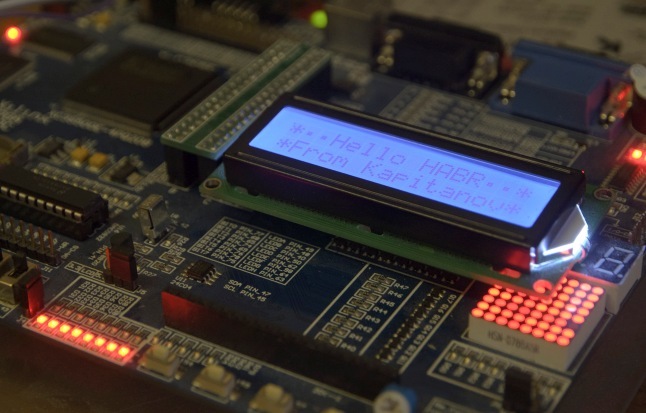

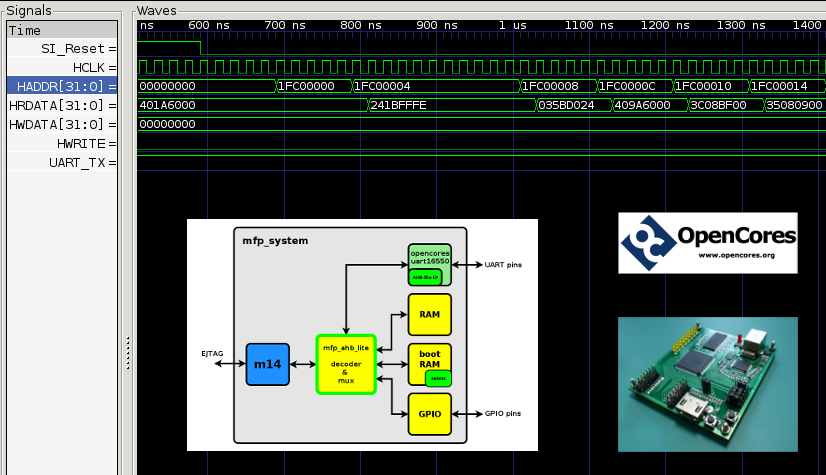

2. Продумана архитектура СИМ, основанная на обычном ПК и плате ускорителе логики. На первоначальном этапе ПК будет использоваться для организации ассоциативной памяти, при помощи быстрой ключ-значения СУБД и обеспечения ввода вывода. Ускоритель логики будет изготавливаться на основе микросхем программируемой логики (FPGA), в которых будут размещаться массивы из двухбитных микроядер и сумматоров для коэффициентов.

3. Разработана система говорящих имён для образов (объектов и действий), основанная на множестве признаков, присущих тому или иному образу. Фактически это новый язык программирования – язык образов (ЯО). Всё в мире, это объекты и действия, имеющие свои уникальные наборы признаков и входящие в состав коллекций (моделей окружения).

Читать полностью »