Всем привет!

Давненько мы ничего не писали. А тем временем...

В тридевятом царстве, в тридесятом государстве, в баварской вотчине, в средневековом городе Нюрнберге проходит выставка под названием Embedded World. Цель выставки — собрать в одном месте производителей, разработчиков, студентов и других заинтересованных граждан. Проходит она три дня — с 23 по 25 февраля.

Сайт выставки: http://www.embedded-world.de

Около 900 участников, примерно 25 тысяч посетителей. Двух дней еле-еле хватает, чтобы понять, что к чему. Поэтому выставка длится три дня :)

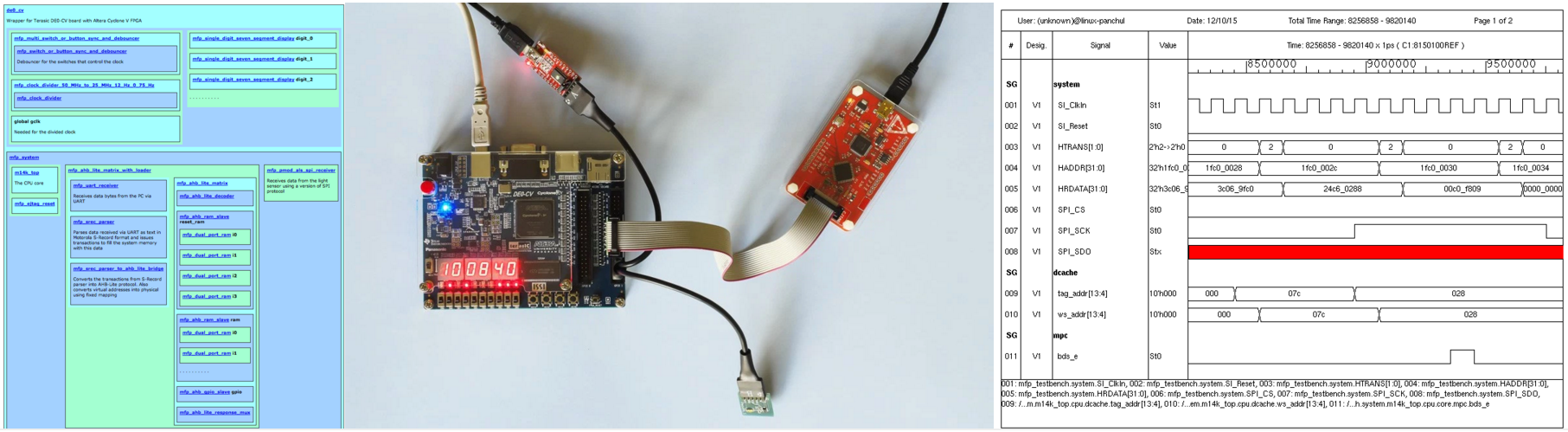

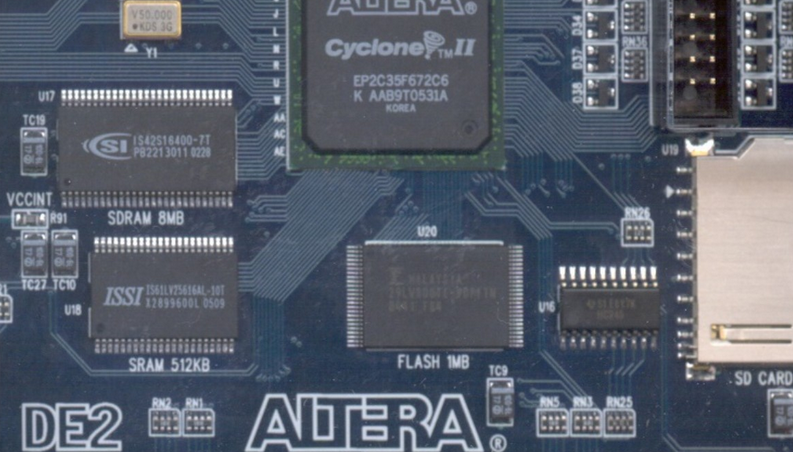

Судьба забрасывает меня на это мероприятие уже не в первый раз: мы с коллегами по НТЦ Метротек посещали выставку в 2013, 2014 и 2015 годах. Именно здесь мы впервые увидели Cyclone V SoC (System On Chip c ARM и FPGA на борту), который впоследствии лёг в основу новых девайсов производства НТЦ Метротек (это — Беркут-ЕТ, EthOnd, BlueSoM, ETL-N). Именно здесь мы нашли производителей корпусов EMKO и наладили с ними сотрудничество, теперь все стоечные приборы (свитч Metrotek X10-24, Беркут-МХ) выглядят единообразно. Здесь мы узнаём о новинках и трендах.

Под катом больше информации об участниках, новых продуктах и просто вещах, которые нам понравились и запомнились.

С фотографиями и ссылками.

Читать полностью »