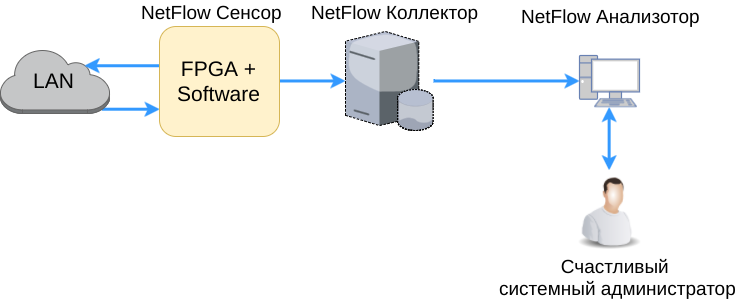

На днях я встретился и взял короткое видеоинтервью у Kathy Giori, Vice President Operations Arduino USA. Мы обсудили с Кати новое веяние, которое уже коснулось и Ардуино-коммьюнити: так как программированию микроконтроллеров с помощью Ардуино уже все более-менее научены, то пора делать следующий шаг: учить школьников использовать язык описания аппаратуры Verilog и микросхемы ПЛИС / FPGA, матрицы логических элементов с изменяемыми функциями. А для того, чтобы сделать освоение FPGA проще, стоит воскресить упражнения с микросхемами малой степени интеграции, популярные в 1970-х, в качестве приквела к современным FPGA. Все это закроет брешь между физикой и программированием, дискретными элементами и микроконтроллерами, транзистором и Ардуино.

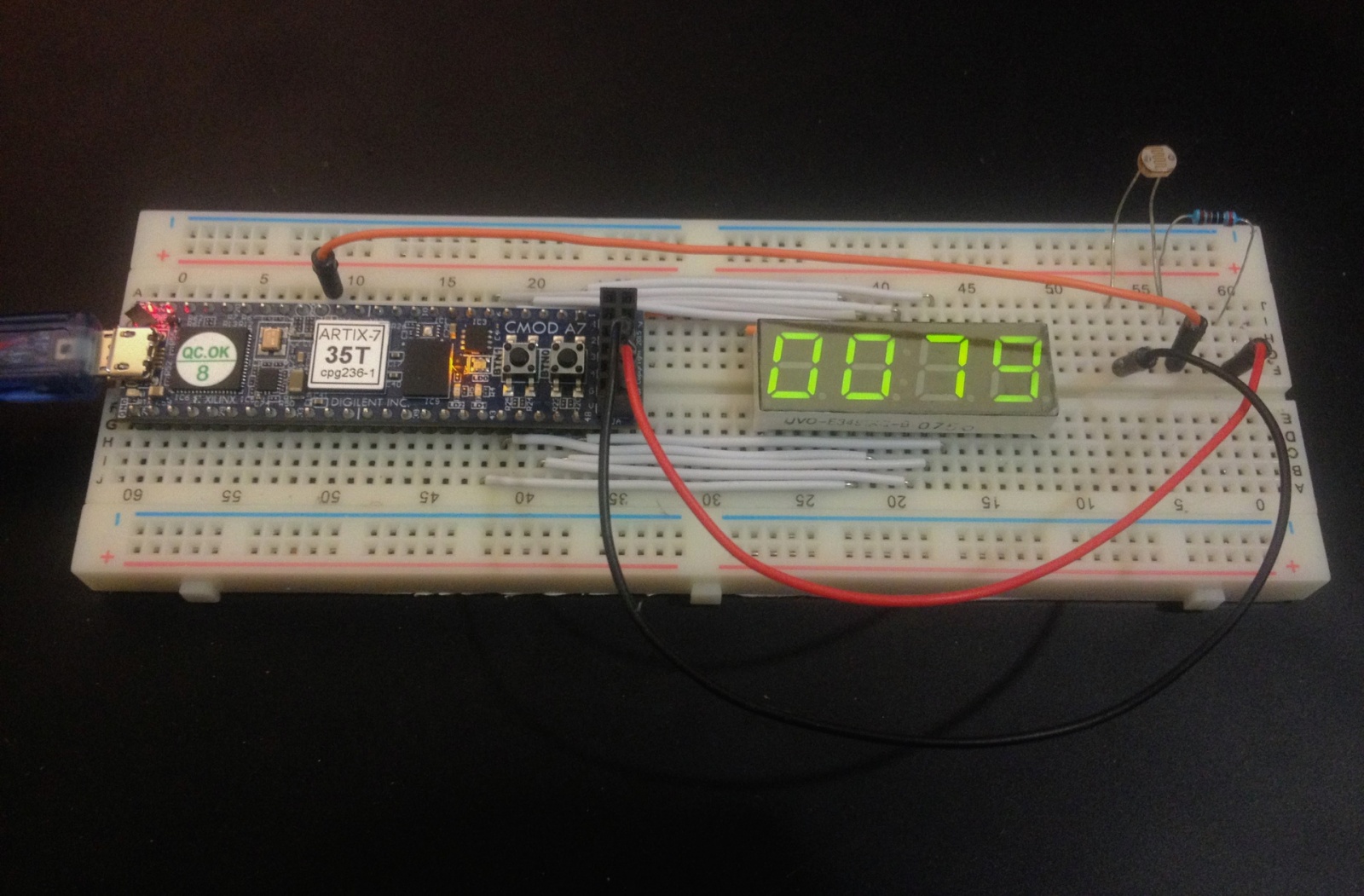

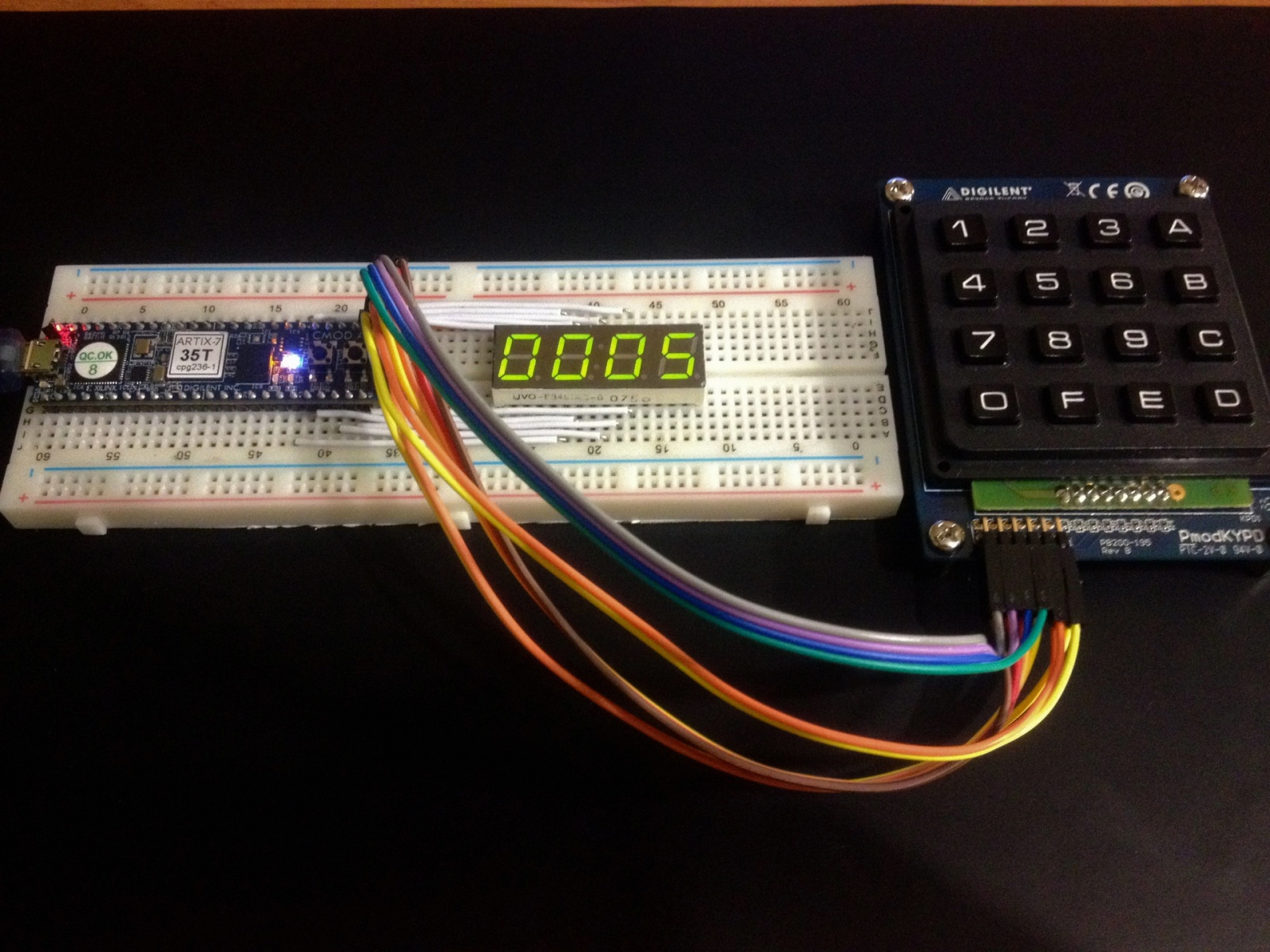

FPGA и платы можно использовать от любого производителя (Xilinx, Altera, Lattice, Digilent, Terasic), все что я пишу ниже, не имеет привязки к той или иной компании.

В разговоре с Кати принимала участие преподаватель Стенфорда Светлана Хутка, которая рассказала Кати об эксперименте по бесплатному обучению школьников использованию FPGA в Киеве, силами преподавателей-энтузиатов из нескольких киевских вузов. После этого я поделился с Кати планами проведения следующего такого эксперимента на известной еще с советских времен летней школе юных программистов в Новосибирске, а также поговорил с другими присутствующими товарищами из Ардуино-коммьюнити о внедрении FPGA в двух школах и одном коледже Silicon Valley.