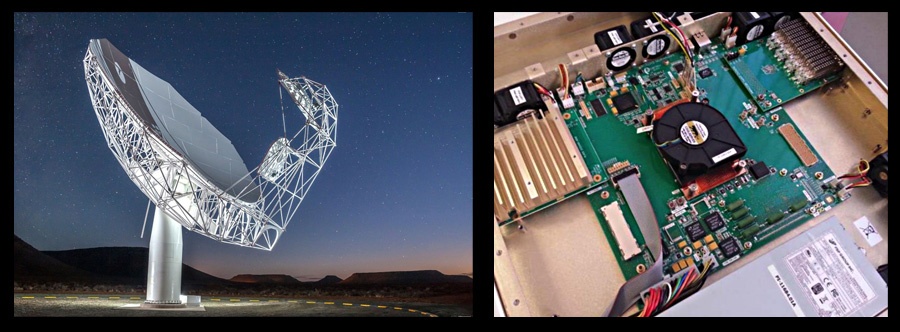

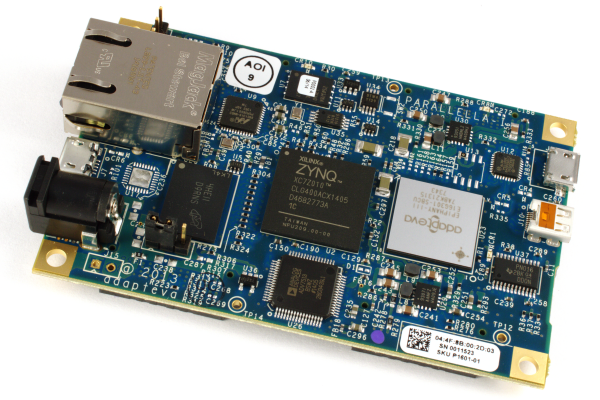

Устройство называется CEPappliance. CEP — от Complex Event Processing, а appliance — (и так должно быть понятно, но на всякий случай) “устройство” с английского.

Затеяли мы его в далеком 2010 году как хобби, трудясь над ним после основной работы долгими вечерами, плавно переходящими в короткие ночи, и по выходным дням. За 5 лет такой работы мы создали 3 прототипа в поисках решения с минимальными задержками и простой моделью программирования логики обработки данных.

В 2015 году мы осознали, что у нас получилось достойное творение, которое позволяет обрабатывать потоки данных с гарантированной задержкой в 2-3 микросекунды. И мы начали искать возможности превратить начатое в коммерческий продукт и, вероятно, перестать работать на “дядю”, заняться только нашим продуктом, посвящая ему все свое время. В конце 2015 мы нашли первого клиента, оставили “дядей” и пустились в “свободное плавание”.

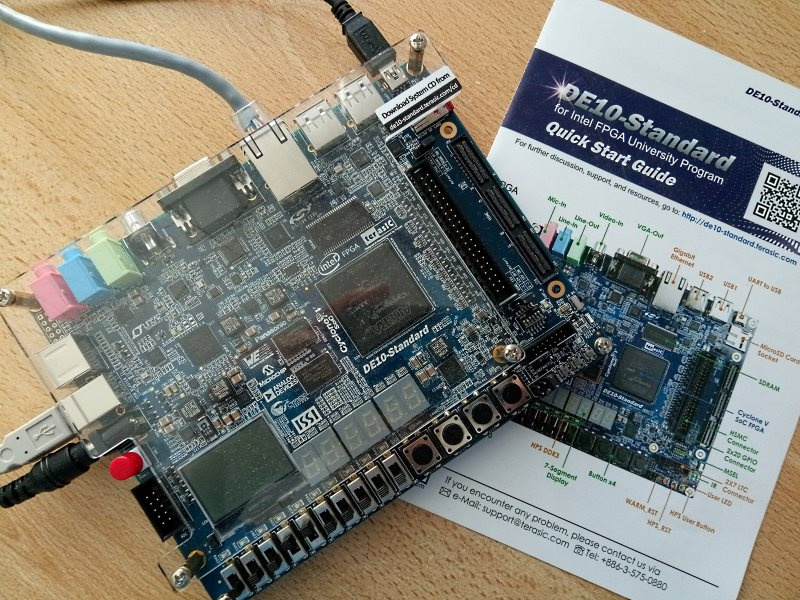

Сегодня мы можем точно сказать, что устройство у нас получилось. Мы еще не реализовали всего задуманного и нам по-прежнему приходится много работать, чтобы добавлять новый функционал, иногда исправлять ошибки. Но наше устройство уже год работает в промышленной эксплуатации.

Читать полностью »