Мы уже 2 года плотно общаемся с HFT трейдерами и разработчиками решений для HFT торговли. И испытываем некоторую неловкость от того, что никто в этой среде открыто не рассказывает о своих технологических успехах. Так как мы делаем устройства на основе FPGA CEPappliance, применимые в том числе для HFT торговли, мы неустанно интересуемся кто и как использует FPGA в этой сфере. Складывается навязчивое впечатление, что FPGA в HFT торговле, как секс у подростков — все о них говорят, но мало кто ими занимается, да еще и успешно.

Читать полностью »

Рубрика «fpga» - 21

Реализация HFT роботов на устройствах CEPappliance

2017-10-27 в 8:57, admin, рубрики: algorithmic trading, fpga, HFT-трейдинг, high performance, pre-trade, risk checks, Анализ и проектирование систем, высокая производительность, Программирование, стартапы; команда; опытСравнение tick-to-trade задержек CEPappliance и Solarflare TCPDirect

2017-10-09 в 19:38, admin, рубрики: algorithmic trading, fpga, HFT-трейдинг, high performance, Исследования и прогнозы в IT, стартапы; команда; опытВ этой статье мы приводим значения задержек, измеренных для двух типов окружений — устройство на основе FPGA CEPappliance (“железка”) и компьютер с сетевой платой Solarflare в режиме TCPDirect, рассказываем как мы эти замеры получили — описываем методику измерения и ее техническую реализацию. В конце статьи есть ссылка на GitHub с полученными результатами и некоторыми исходниками.

Как нам кажется, полученные нами результаты могут быть интересны высокочастотным трейдерам, алготрейдерам и всем неравнодушным к обработке данных с малыми задержками.

Читать полностью »

Обзор плат на SoC ARM+FPGA. Часть 2. Мир Intel (Altera)

2017-09-26 в 0:34, admin, рубрики: arduino, arm cortex a9, cyclone v soc, diy или сделай сам, fpga, Железо, Электроника для начинающихЧасть 1. Мир Xilinx

Часть 2. Мир Intel (Altera)

Продолжаем обзор девелоперских плат на основе SoC с ядром ARM. На этот раз мы рассмотрим платы на SoC Cyclone V. Это не единственный SoC компании Intel, есть ещё Arria V, Arria 10 и Stratix 10, но цена плат на их основе вас точно не обрадует.

К сожалению, плат на основе Cyclone V гораздо меньше, чем на Xilinx Zynq, и в основном они производятся одной компанией, Terasic. Есть ещё плата Arrow SocKit, но она полностью эквивалентна плате Terasic SoCKit. Основная информация по платам Terasic сосредоточена на сайте rocketboards.org. Там можно скачать разные полезные материалы, образы дистрибутивов Linux, там же находится форум. Форум довольно вялый, и на получение поддержки там я бы не рассчитывал, но лучше что-то, чем ничего.

Также компания Terasic продаёт некоторые платы по сниженной цене при наличии студенческого билета («academic price»). Насколько это реально для российских студентов, я не знаю, но если кто-то имел опыт такой покупки, будет интересно узнать. Пишут, что, например, Digilent при запросе покупки по академической цене отсылает к российсим дистрибьюторам, у которых цены завышены в 2-3 раза. Может быть, Terasic поступает иначе.

Кроме продукции компании Terasic мы рассмотрим также две платы производства компании EBV. Другие компании, выпускающие продукцию на Cyclone V, делают в основном модули SoM, а не девборды, и в обзор не попали.

Обзор плат на SoC ARM+FPGA. Часть первая. Мир Xilinx

2017-09-19 в 16:01, admin, рубрики: arduino, arm cortex a9, diy или сделай сам, fpga, zynq-7000, Железо, Электроника для начинающихЧасть 1. Мир Xilinx

Часть 2. Мир Intel

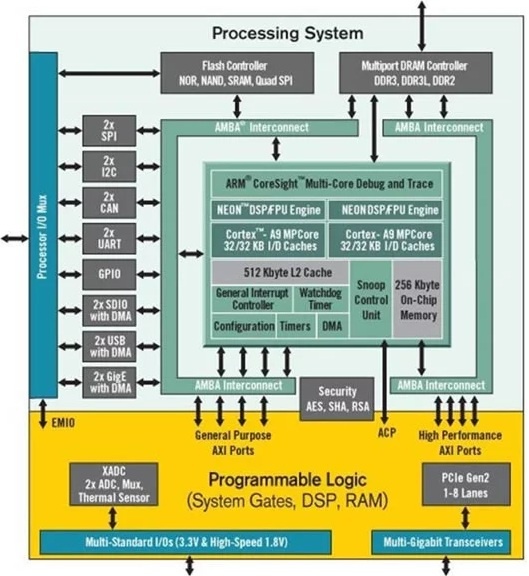

В опубликованном ранее переводе обзора 98 «хакерских» плат немалый интерес аудитории вызвали платы на базе SoC, сочетающих в себе ядра ARM и FPGA, такие, как Parallella. И это неудивительно, ведь такая комбинация даёт воистину потрясающие возможности по сравнению с «просто» процессором или «просто» FPGA. На таких SoC можно строить системы, сочетающие в себе алгоритмичски сложные задачи, поддержку сетевых стеков, GUI и прочих вещей, проще поддающихся реализации на процессоре, и задачи, требующие жесткого реального времени, обработки сигналов, обработки изображений и другие задачи, для реализации которых удобны FPGA. Разумеется, для многих задач можно использовать простые FPGA (возможно, включив в них IP-ядро процессора типа NIOS II или MicroBlaze), многие задачи можно решить на процессоре достаточной мощности, используя операционные системы реального времени (типа RTEMS), но всё же, SoC являются в настоящее время очень привлекательным вариантом для решения множества задач, как в профессиональных областях, так и для хобби.

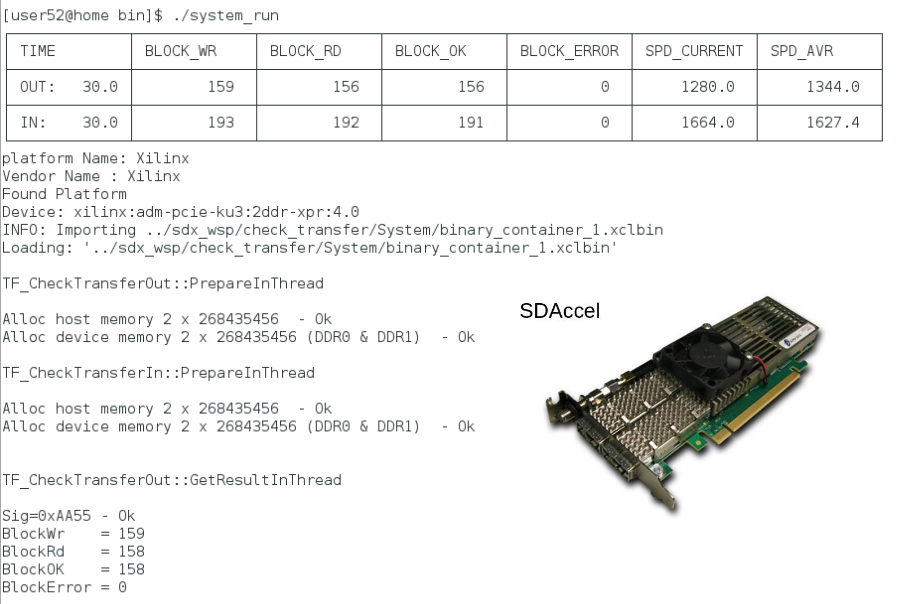

SDAccel — проверяем передачу данных

2017-09-13 в 23:57, admin, рубрики: fpga, gpgpu, opencl, sdaccel, xilinx, высокая производительность, параллельное программирование

В предыдущей статье «SDAccel – первое знакомство» я попытался описать основы применения OpenCL на ПЛИС Xilinx. Теперь настало время поделиться результатами экспериментов по передаче данных на модуле ADP-PCIe-KU3. Проверяется передача данных в обоих направлениях. Исходный код программ размещён на GitHub: https://github.com/dsmv/sdaccel

Экскурсия по Музею Истории Компьютеров в Калифорнии, с пользой для разработки. Часть 1. ENIAC, Stretch, CDC6600, IBM-360

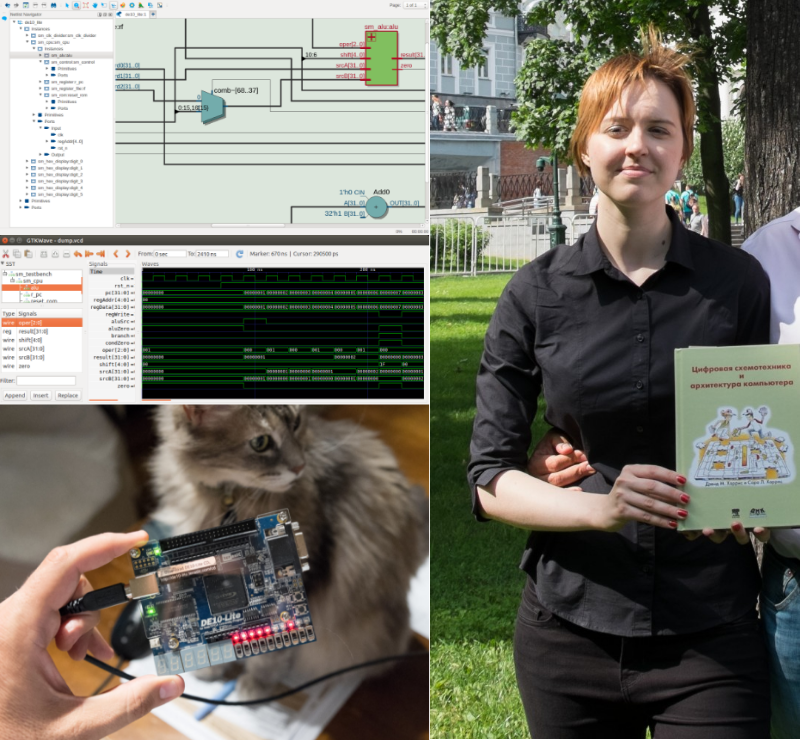

2017-09-05 в 7:28, admin, рубрики: Altera, CDC 6600, ENIAC, fpga, IBM 7030, IBM 704, IBM Stretch, IBM System/360 Model 91, IBM/360, Intel FPGA, Lattice, NEAC 2203, NEC SX-3/44, OS/360, silicon valley, SystemVerilog, vhdl, xilinx, алгоритм Томасуло, Алгоритмы, архитектура фон-Немана, высокая производительность, ЕС ЭВМ, калифорния, Киево-Могилянская Академия, Мифический человеко-месяц, МИЭМ НИУ ВШЭ, Новосибирский ТГУ, параллельное программирование, ПЛИС, системное программирование, Фредерик Брукс, Элвис, япония, Япония может сказать NOГоспода! Сегодня мы пройдемся с сибирской девушкой Ириной по Музею истории компьютеров в Маунтин-Вью, Калифорния. Причем пройдемся не как туристы, а для принесения пользы России. Я уже писал в предыдущем посте, что один из эффективных способов для студента изучить проектирование процессоров — это взять какой-нибудь древний, но поучительный процессор, найди документацию по его архитектуре (и какую-нибудь информацию по его микроархитектуре), и спроектировать аналог этого процессора на языке описания аппаратуры SystemVerilog (или VHDL, если он вам больше нравится), после чего реализовать процессор на плате ПЛИС / FPGA (какой именно, не важно — Altera / Intel FPGA, Xilinx или Lattice). В качестве учебника для такого упражнения вы можете начать с Харрис & Харрис, после чего продолжить с книгами для более продвинутой стадии обучения, например Шень-Липасти.

Каким образом все это принесет пользу России? Под такие проекты мы собираемся раздавать FPGA платы на конференции которая пройдет 18-22 сентября в Томске. Туда приедут представители МГУ, МФТИ, МИЭТ, МЦСТ, Imagination Technologies, National Instruments итд. Они будет обсуждать, как обновить программу университетов, чтобы сегодняшние студенты через несколько лет проектировали росийские чипы на уровне передовых западных компаний. Там также будет школа-семинар, на которой будут обсуждать, как делать учебные процессоры — начиная от простейшего schoolMIPS от Станислава Жельнио sparf.

Вот первая фотография из музея в Маунтин-Вью — на ней помимо Ирины и ракеты в центре виден небольшой ящичек. Это бортовой компьютер космической станции «МИР» , который проектировали инженеры советского объединения «ЭЛАС», которое трансформировалось в современную зеленоградскую компанию «ЭЛВИС»:

Итак, темы для учебных проектов — начиная из дремучих десятилетий середины XX века:

Читать полностью »

Следущие шаги в черной магии процессоростроения после того, как вы освоили Харрис & Харрис

2017-08-22 в 7:44, admin, рубрики: asic, fpga, fpga/asic, mips, MIPSfpga, schoolmips, Verilog, vhdl, Анализ и проектирование систем, ассемблер, вшэ, высокая производительность, мгу, микроэлектроника, МИФИ, МИЭМ, нгту, программирование микроконтроллеров, Профессиональная литератураНедавно вышло еще одно печатное издание книжки Харрис & Харрис на русском языке. Это широкоохватывающий ликбез про то, как проектируют микросхемы в компаниях типа Apple и Intel (методология проектирования на уровне регистровых передач с использованием языков описания аппаратуры). До этого печатного издания вышло бесплатное электронное издание этой же книжки, которое стало вирусным — его скачивания дважды завалили британский сайт Imagination Technologies, а посты о книжке на Хабре и Гиктаймс собрали более 300,000 просмотров (1, 2, 3, 4, 5 ). История перевода книжки на русский тоже довольно поучительна — он начался как общественный проект группы энтузиастов: преподавателей российских и украинских университетов, а также русских сотрудников компаний как в Silicon Valley (MIPS, AMD, Synopsys, Apple, NVidia ...) так и в России (НИИСИ, МЦСТ, Модуль ...). Когда вышло первое печатное издание на русском языке, его тоже довольно быстро раскупили и пожаловались, что оно черно-белое. Поэтому следующий принт был цветной, улучшенного качества.

Теперь возникает вопрос: ну хорошо, вы приобрели или скачали бесплатно книжку, поняли основы цифровой схемотехники, языков описания аппаратуры Verilog и VHDL, приобрели вкус писания на ассемблере и разобрались с организацией простейшего конвейерного микропроцессора, а также как все это стыкуется с периферийными устройствами и встроенным программированием. Что делать дальше?

На снимке — Татьяна Волкова, сотрудница образовательных программ компании Samsung в Московском Физико-Техническом Институте

Читать полностью »

MIPSfpga – практический опыт

2017-08-17 в 16:56, admin, рубрики: C, fpga, mips, MIPS microAptiv UP, MIPSfpga, SoC, Verilog, Анализ и проектирование систем, образование, перевод, программирование микроконтроллеров, системное программирование

Перевод коллективной статьи Practical experiences based on MIPSfpga, не так давно представленной Сарой Харрис на симпозиуме в Торонто. Приводится подробное описание MIPSfpga 2.0, релиз которой состоялся 3 июля 2017 года. Основное, на мой взгляд, отличие по сравнению с версией 1.3: пакет лабораторных работ расширен набором, ориентированным на внутреннюю работу процессора. Так что, если вы хотите узнать, как работает современное ядро, то MIPSfpga 2.0 — это ваш выбор для качественного самообразования. Крайне полезной данная статья будет для преподавателей ВУЗов — подробно и с примерами рассматривается вопрос интеграции MIPSfpga 2.0 в учебный процесс, включая ее соответствие Методическим рекомендациям IEEE/ACM для программ бакалавриата в области вычислительной техники.

Исследование асинхронной схемы в ModelSim

2017-08-15 в 7:51, admin, рубрики: fpga, modelsim, Verilog, асинхронные схемы

Прочитал статью FPGA/Асинхронный дешифратор от ajrec.

Я сперва прочитал и ничего не понял, а потом прочитал еще раз и опять ничего не понял. На самом деле я прочитал уже все статьи ajrec про асинхронные схемы и должен констатировать, что мало понимаю, что это вообще такое (хотя считаю, что опыт проектирования в FPGA у меня есть).

В комментариях к статьям автор в основном получает минусы, народ посмеивается и кажется так же не понимает, как и я.

Честно говоря, я всегда с любопытством смотрю на проекты, которые «не такие, как все». Я считаю, что только такие проекты имеют шанс либо глубоко провалиться, либо высоко взлететь. Если делаешь что-то так же, как и сотни других разработчиков, то идешь проторенной дорогой, здесь легко и комфортно. Сделать шаг в сторону и пойти своей тропой могут далеко не все.

Я попробовал разобраться в проекте асинхронного дешифратора и по крайней мере сделать временную симуляцию кода в ModelSim. Далее о том, что из этого получилось.Читать полностью »

Асинхронный дешифратор

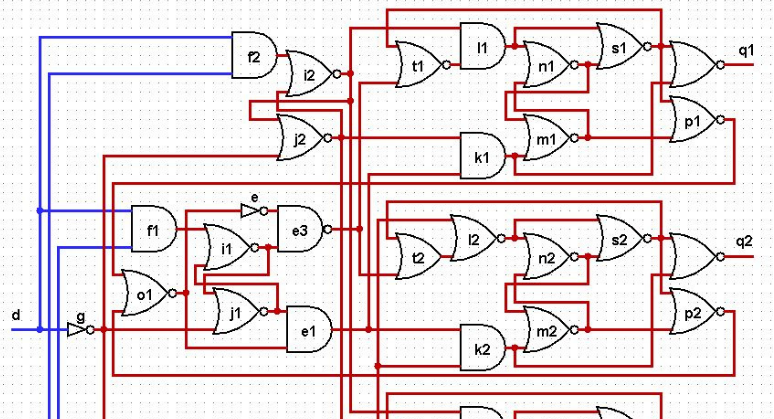

2017-08-08 в 13:22, admin, рубрики: fpga, асинхронные схемы, асинхронный дешифраторКак и обещал в предыдущей статье, речь в этой статье пойдет о представлении в асинхронном виде операций над адресами. В качестве примера опишу операцию дешифрации адреса. Сразу же хочу предупредить инсинуации, с которыми столкнулся после опубликования предыдущей статьи. Речь пойдет о целиком и полностью асинхронном устройстве. И прошу, не надо ссылаться на реферат узбекского университета. Якобы асинхронный дешифратор можно получить из синхронного с помощью нехитрых манипуляций. Заодно вопрос тем, кто утверждает, что асинхронный процессор произведен 20 лет назад. Как это удалось без асинхронного дешифратора?

Итак, об асинхронном дешифраторе. После размышлений я пришел к выводу, что единственный вменяемый путь синтеза асинхронного дешифратора это поэтапное удвоение разрядности адреса с помощью схемы надстройки над двумя дешифраторами вдвое меньшей разрядности. Доказать что альтернативного пути нет я не берусь. Но могу утверждать что альтернативный путь (если он есть) куда более затратен по количеству добавляемых новых сигналов.

Ввиду изложенного, речь в этой статье пойдет о двухразрядном дешифраторе. Как удвоить разрядность асинхронного дешифратора, тема следующей статьи.