Аннотация

В статье рассмотрен режим работы Vivado, позволяющий вносить изменения в проект на уровне редактирования списка соединений (в дальнейшем – нетлиста). Описаны как сам режим ECO, так и некоторые нюансы, которые появляются во время работы в нём. Приведён демонстрационный пример и описана полная последовательность действий для получения результата, в работоспособности которой может убедиться каждый желающий. Статья будет полезна для «общего развития» FPGA-разработчикам, а особенно — тем, кто часто отлаживает проекты в Logic Analyzer. Надеюсь, работа в этом режиме вызовет интерес у разработчиков, работающих с большими кристаллами, время компиляции в которых может достигать часов (а то и десятков часов), поскольку в этом режиме время, затрачиваемое на имплементацию, при внесении изменений в нетлист может сократиться до буквально пары минут.

Оглавление

- Аннотация

- Введение

- 1. ECO: краткий обзор

- 2. Design Сheckpoint

- 3. Разработка тестового проекта

- 3.1. Создание проекта

- 3.2. Создание и добавление HDL файлов в проект

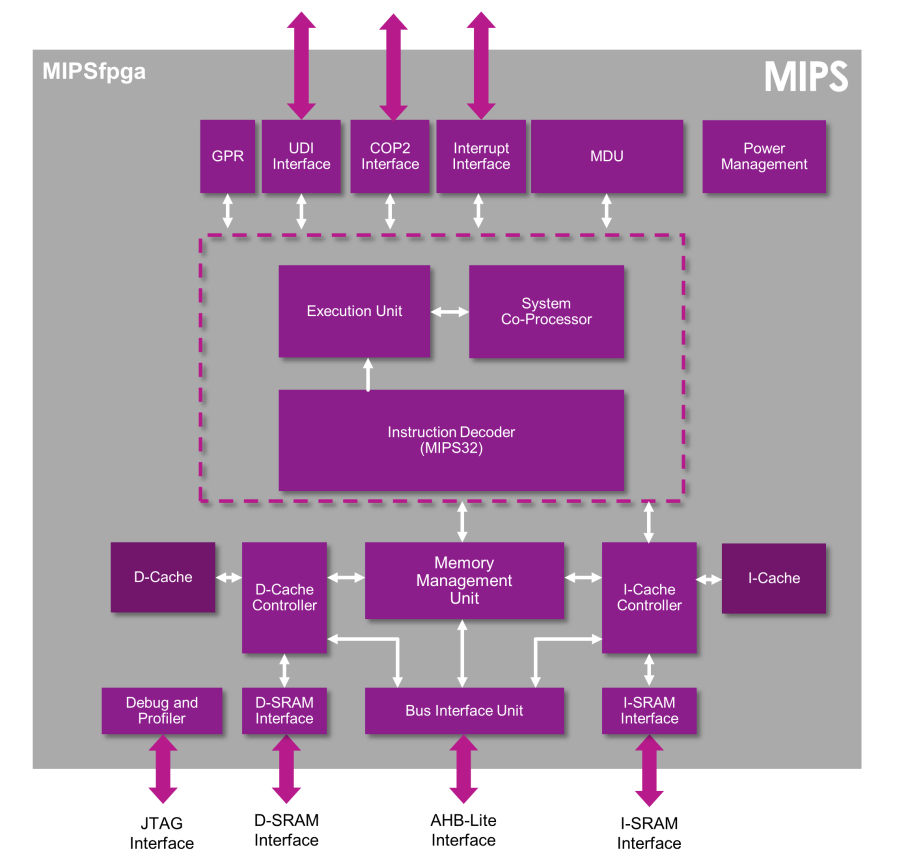

- 3.3.Создание проекта MicroBlaze и работа в IP Integrator

- 3.4.Синтез и имплементация

- 3.5.Написание программы для MicroBlaze

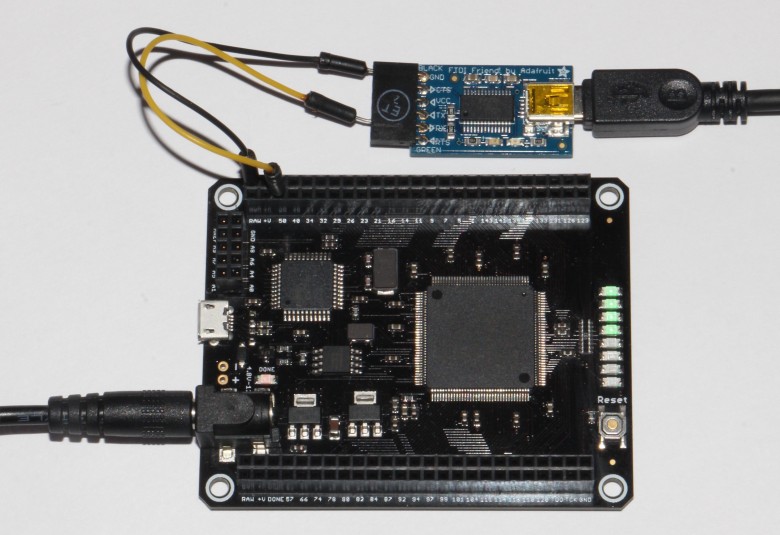

- 3.6.Запуск программы и отладка

- 4. Переход в режим ECO

- 5. ECO: описание интерфейса

- 6. Внесение изменений в проект

- 6.1. Создание новых элементов в нетлисте

- 6.2. Изменение свойств/параметров компонентов

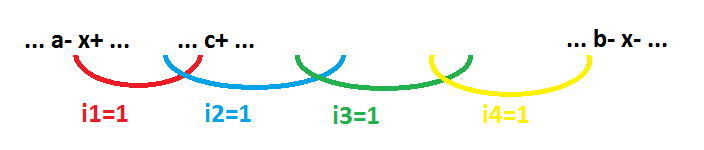

- 6.3. Подключение других цепей к пробникам и ILA

- 6.4. Замена портов ввода/вывода

- 7. Сравнительный анализ

- 8. Заключение

- 9. Домашнее задание

- Библиографический список