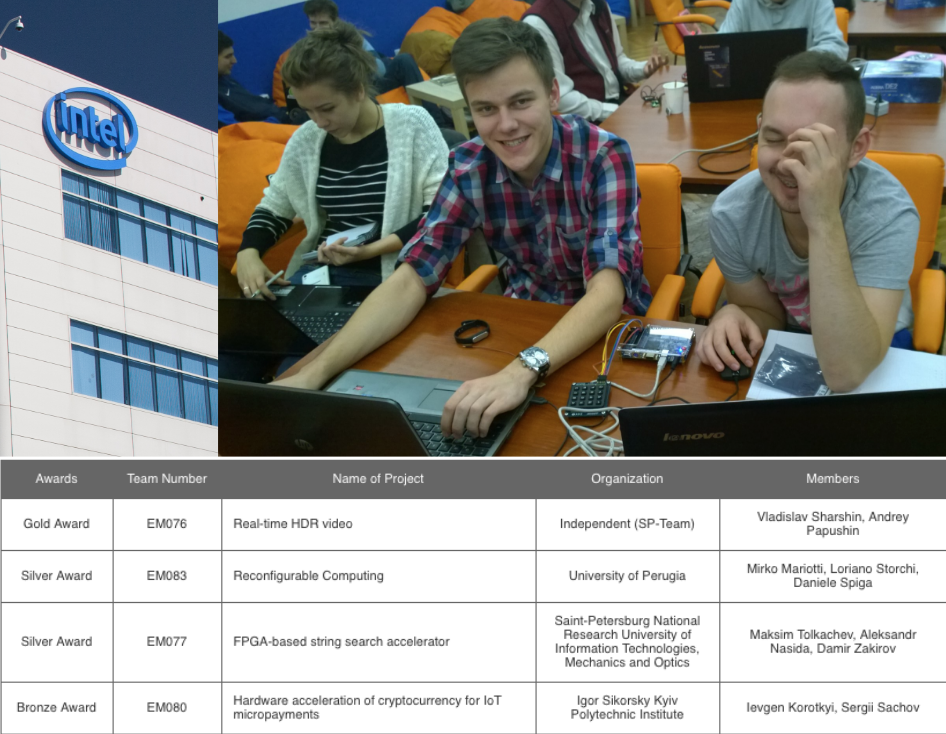

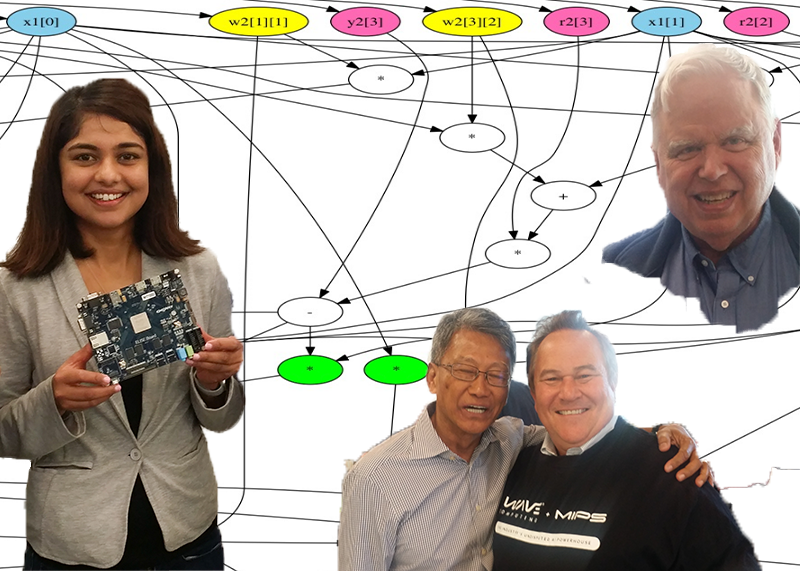

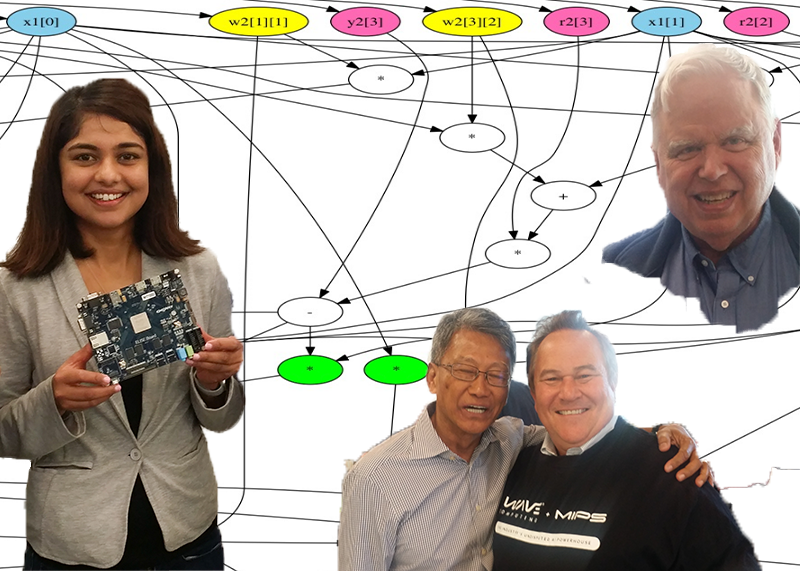

Завтра будут официальные пресс-релизы о слиянии старожила Silicon Valley, компании MIPS, с молодой AI компанией Wave Technology. Информация об этом событии просочилась в СМИ вчера, и вскоре CNet, Forbes, EE Times и куча хайтек-сайтов вышла со статьями об этом событии. Поэтому сегодня Derek Meyer, президент объединенной компании (на фото снизу справа), сказал «ладно, распостраняйте инфо среди друзей» и я решил написать пару слов о технологиях и людях, связанных с этим событием.

Главный инвестор в MIPS и Wave — миллиардер Dado Banatao (на фото снизу в центре слева), который еще в 1980-х основал компанию Chips & Technoilogies, которая делала чипсеты для ранних персоналок. В Wave+MIPS есть и другие знаменитости, например Стивен Джонсон (на фото справа вверху), автор самого популярного C-компилятора начала 1980-х годов. MIPS хорошо известен и в России. В руках дизайнерши Смрити (на фото слева) плата из Зеленограда, где находятся лицензиаты MIPS Элвис-НеоТек и Байкал Электроникс.

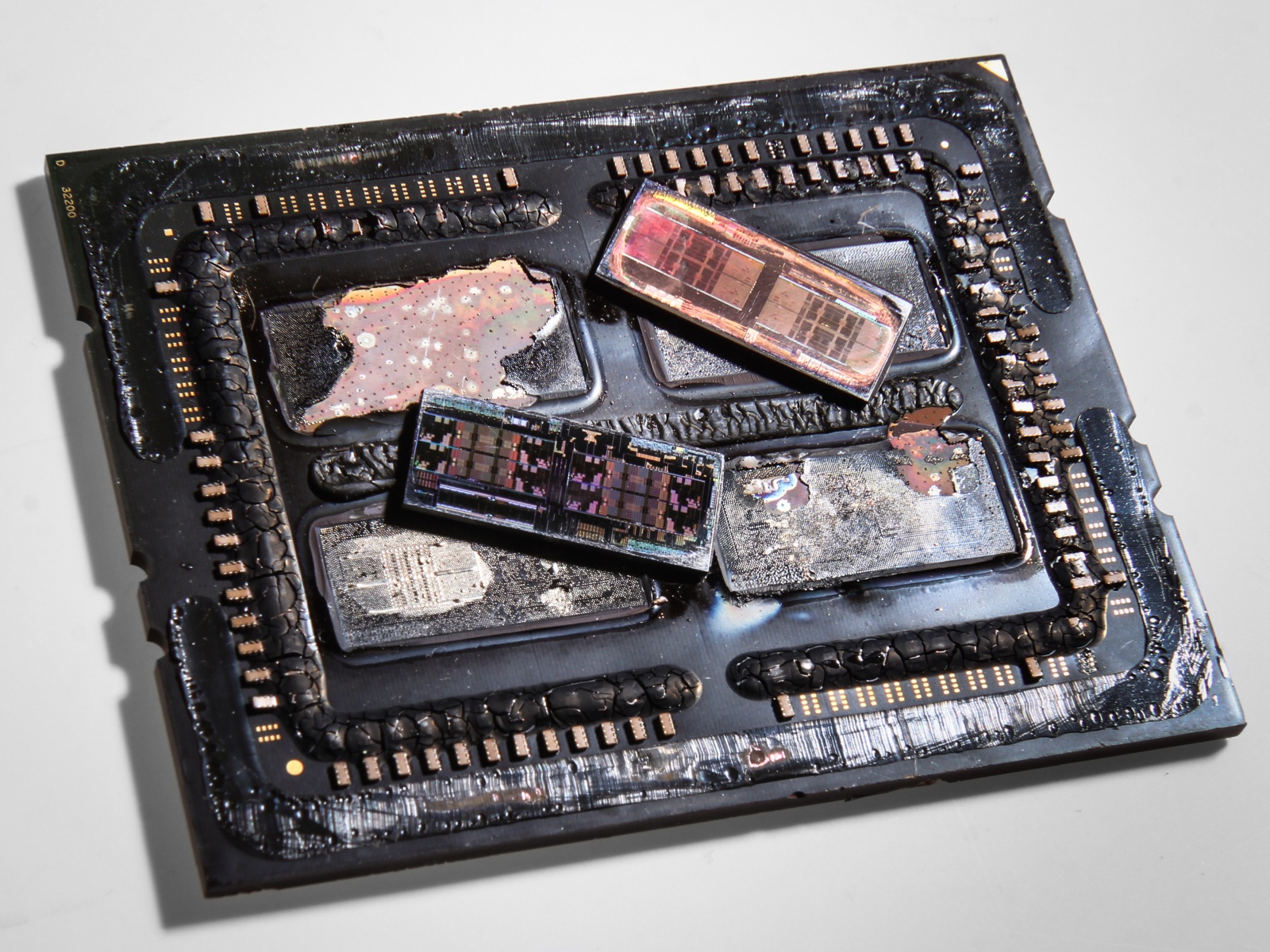

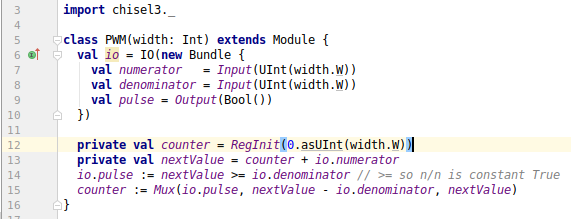

Wave уже выпустила чип, который состоит из тысяч вычислительных блоков, по сути упрощенных процессоров. Эта конструкция оптимизирована для очень быстрых вычислений нейронных сетей. У Wave есть компилятор, который превращает dataflow граф в файл конфигурации для этой структуры.

Объединенная компания создаст чип, который состоит из смеси таких вычислительных блоков и многопоточных ядер MIPS. Сейчас Wave продает свою технологию в виде ящика для дата-центров, для вычислений нейронных сетей в облаке. Следующие чипы будут использоваться во встроенных устройствах.

Читать полностью »