В статье описан очередной велосипед процессор.

Вместо обычных RISC/СISC процессор не обладает набором инструкций как таковым, только единственная инструкция копирования.

Подобные процессоры есть у Maxim серия MAXQ.

Рубрика «fpga» - 14

Ещё один простой процессор на verilog

2018-12-16 в 21:55, admin, рубрики: diy или сделай сам, fpga, Lua, программирование микроконтроллеров, Процессоры, Электроника для начинающихДесятиклассница из Сибири хочет стать проектировщицей процессоров. Почему бы ей не сделать нейроускоритель на ПЛИС?

2018-12-07 в 8:50, admin, рубрики: fpga, Verilog, vhdl, высокая производительность, искусственный интеллект, машинное обучение, нейросети, образование, олимпиадное программирование, ПЛИС, Электроника для начинающихВчера мне пришло письмо от десятиклассницы из Сибири, которая хочет стать разработчицей микропроцессоров. Она уже получила некоторый результат в этой области — добавила инструкцию умножения в простейший процессор schoolMIPS, синтезировала его для ПЛИС Intel FPGA MAX10, определила максимальную частоту и повышение производительности простых программ. Все это она сначала делала в деревне Бурмистрово Новосибирской Области, а потом на конференции в Томске.

Теперь Даша Криворучко (так зовут десятиклассницу) переехала жить в московский интернат и спрашивает у меня, чего бы ей еще спроектировать. Я думаю, что на этом этапе карьеры ей стоит спроектировать аппаратный ускоритель нейросетей на основе систолического массива для умножения матриц. Использовать язык описания аппаратуры Verilog и ПЛИС Intel FPGA, но не дешевенький MAX10, а что-нибудь подороже, чтобы вместить большой систолический массив.

После этого сравнить производительность аппаратного решения с программой, работающей на процессоре schoolMIPS, а также с программой на Питоне, работающей на десктопном компьютере. В качестве тестового примера использовать распознавание цифр с небольшой матрицы.

RAM with Simple direct-mapped cache simulation on FPGA in Verilog

2018-12-06 в 14:11, admin, рубрики: cache, fpga, fpga дизайн, ram, simulation, testbench, VerilogSimple direct-mapped cache simulation on FPGA

This article is a part of a course work for first year bachelor students of Innopolis University. All work is done in a team. The purpose of this article is to show an understanding of the topic, or to help to understand it using simulation.

Principle of work but from the user side should look like:

- To write any data in memory, you need to access the RAM with data and address in which we want to write.

- To access the data, we have to adress to cache. If the cache cannot find the necessary data, then it accesses the RAM by copying data from there.

When working with Verilog, it should be understood that each individual block of the program is represented as a module. As you know, the cache is not an independent part of fast memory, and for its proper operation it needs to take data from another memory block — RAM. Therefore, in order to simulate the work of the cache at the FPGA, we have to simulate whole RAM module which includes cache as well, but the main point is cache simulation.

The implementation consists of such modules:

- ram.v — RAM memory module

- cache.v — Cache memory module

- cache_and_ram.v — module that operates with data and memory.

- testbench.v and testbench2.v — module to show that main modules work perfectly.

Musical box and rotary encoder on FPGA board

2018-11-30 в 8:19, admin, рубрики: fpga, FPGA Cyclone IV, Innopolis University, Verilog, программирование микроконтроллеровIntroduction

We are the first year students studying Computer Science in Innopolis University and we would like to share our experience in developing a Verilog program to create the coolest (well, at least, the loudest) rotary encoder ever on an FPGA board.

In this article, you will find a wonderful story about our project, the hardware, software we used and some background theory regarding rotary encoder and creating sounds in FPGA’s buzzer. Finally, we will provide a link to a github repository where a reader can access the source code. We hope you will like the project and it will inspire you to make something similar.

So, let’s start!

Hardware and Software

A Practical Implementation of the Switching Generator Using Verilog HDL

2018-11-29 в 7:29, admin, рубрики: fpga, FPGA AlteraAbstract

Linear feedback shift registers are an excellent tool for implementing a pseudo random bit generator in hardware; they inhibit a simple and efficient electronic structure. Further, they are capable of producing output sequences with large periods and good statistical properties. However, standard LFSRs are not cryptographically secure, since the output sequence can be uniquely predicted given a small number of key stream bits using Berlekamp-Massey algorithm. Several methods have been proposed to destroy the linearity inherent in LFSR design. These methods include nonlinear combination generators, nonlinear filter generators, and clock controlled generators. Nevertheless, they remain vulnerable to many attacks such as side channel attacks and algebraic attacks. In 2015, a new clocked controlled generator, called the switching generator, was proposed. This new generator has been proven to be resistant to algebraic attacks and side channel attacks, while preserving efficiency and security requirements. In this project, we present a design of the switching generator using Verilog HDL.

Читать полностью »

Real-time edge detection using FPGA

2018-11-28 в 8:03, admin, рубрики: edge detect, electronics, fpga, FPGA Cyclone IV, image processing, Innopolis University, Verilog, АлгоритмыIntroduction

Our project implements a real-time edge detection system based on capturing image frames from an OV7670 camera and streaming them to a VGA monitor after applying a grayscale filter and Sobel operator. Our design is built on a Cyclone IV FPGA board which enables us to optimize the performance using the powerful features of the low-level hardware and parallel computations which is important to meet the requirements of the real-time system.

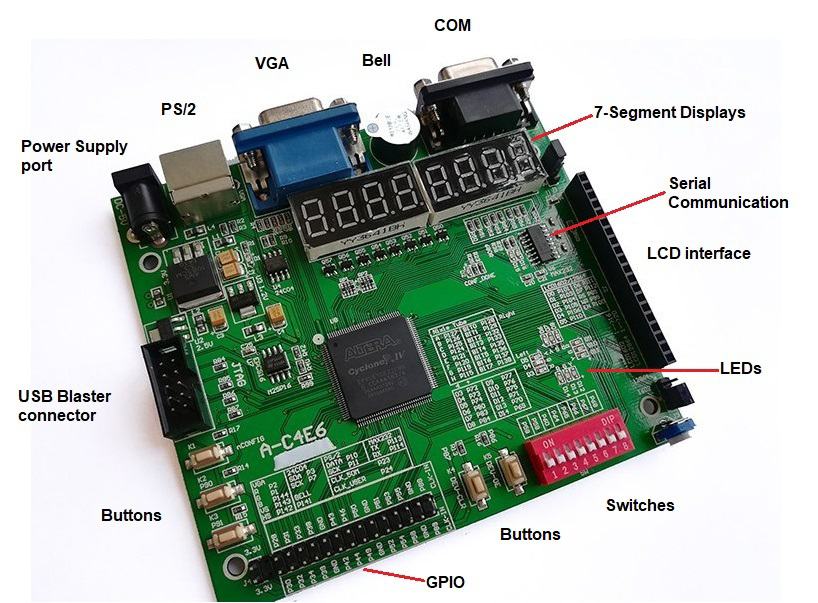

We used ZEOWAA FPGA development board which is based on Cyclone IV (EP4CE6E22C8N). Also, we used Quartus Prime Lite Edition as a development environment and Verilog HDL as a programming language. In addition, we used the built-in VGA interface to drive the VGA monitor, and GPIO (General Pins for Input and Output) to connect the external hardware with our board.

The Snake game for FPGA Cyclone IV (with VGA & SPI joystick)

2018-11-27 в 10:10, admin, рубрики: digital, fpga, game development, Innopolis University, joystick, snake, Verilog, VGA, Игры и игровые приставкиIntroduction

Do you remember the snake game from childhood, where a snake runs on the screen trying to eat an apple? This article describes our implementation of the game on an FPGA1.

Figure 1. Gameplay

Написание простого процессора и окружения для него

2018-11-21 в 16:23, admin, рубрики: C, fpga, Verilog, программирование микроконтроллеров, системное программирование, Создание процессораЗдравствуйте! В этой статье я расскажу какие шаги нужно пройти для создания простого процессора и окружения для него.

Модель разработки на примере Stack-based CPU

2018-11-19 в 19:03, admin, рубрики: fpga, java, own language, Verilog, ПрограммированиеВозникал ли у вас когда-нибудь вопрос "как работает процессор?". Да-да, именно тот, который находится в вашем в ПК/ноутбуке/смартфоне. В этой статье я хочу привести пример самостоятельно придуманного процессора с дизайном на языке Verilog. Verilog — это не совсем тот язык программирования, на который он похож. Это — Hardware Description Language. Написанный код не выполняется чем-либо (если вы не запускаете его в симуляторе, конечно), а превращается в дизайн физической схемы, либо в вид, воспринимаемый FPGA (Field Programmable Gate Array).

Introduction

We have created a synthesizable verilog code for calculating an integer cube root of an integer number via binary search algorithm. This code had been tested on Cyclone IV FPGA board. Here you can read about implementation and understand how things works.

Github link: Cube root

Читать полностью »