Здравствуйте. Меня зовут Дмитрий. Сегодня мы научимся работать с SDRAM памятью и нарисуем множество Мандельброта на экране.

Данная статья является продолжением статьи Создание видеокарты Бена Итера на FPGA чипеЧитать полностью »

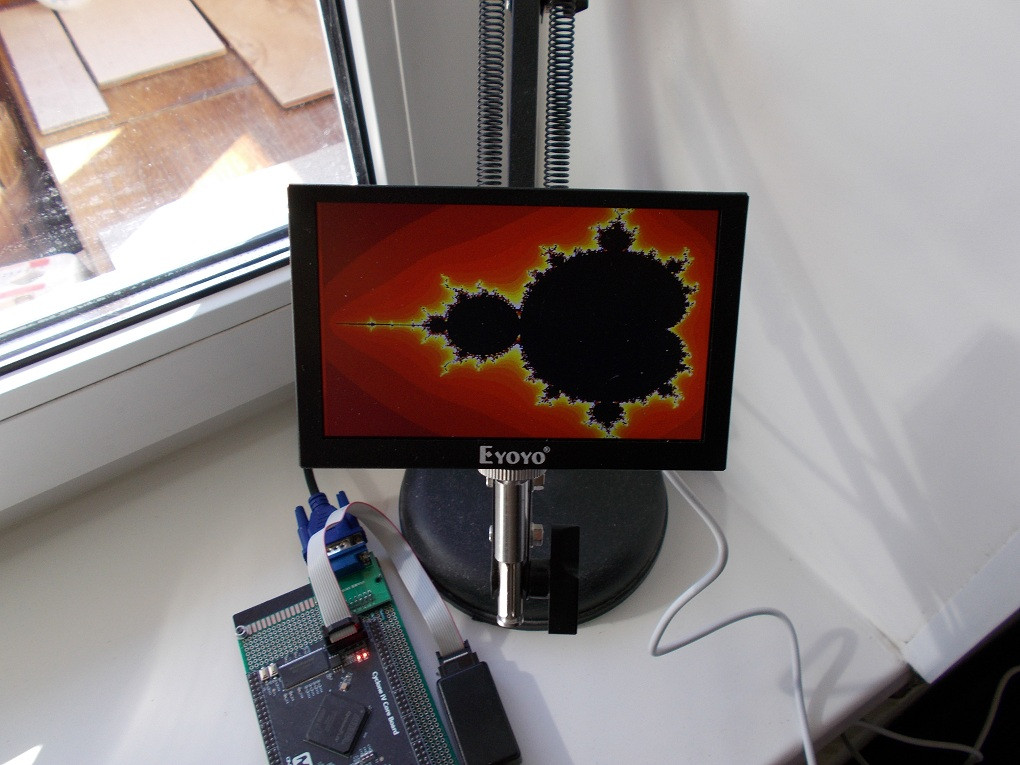

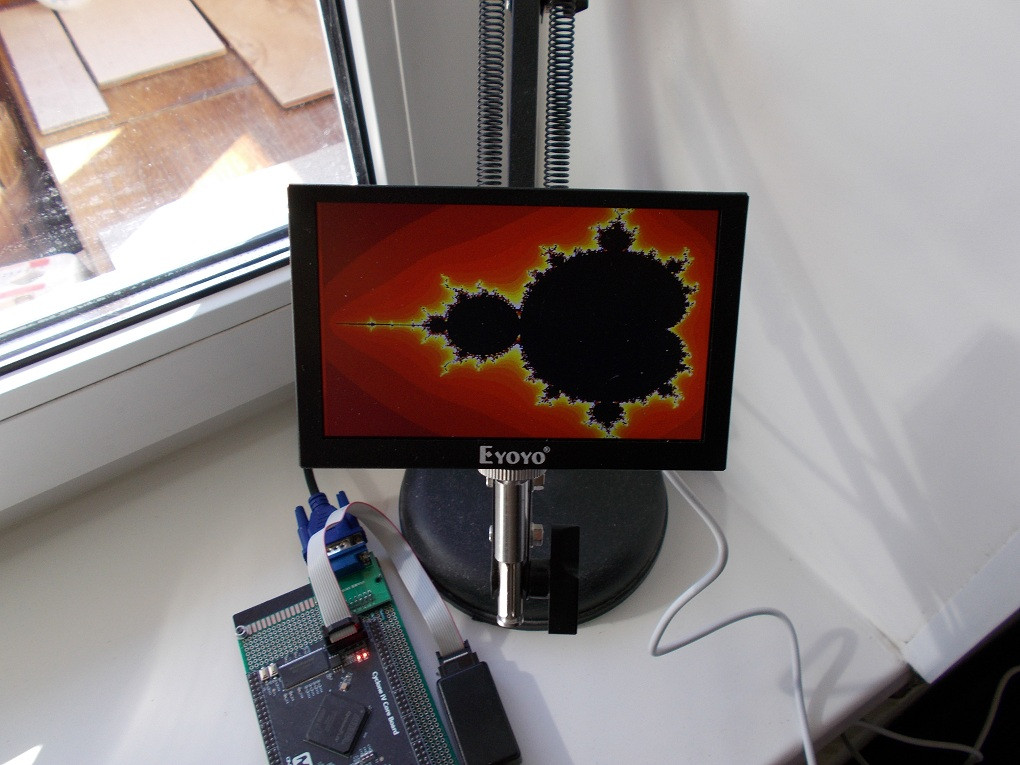

Здравствуйте. Меня зовут Дмитрий. Сегодня мы научимся работать с SDRAM памятью и нарисуем множество Мандельброта на экране.

Данная статья является продолжением статьи Создание видеокарты Бена Итера на FPGA чипеЧитать полностью »

Совсем недавно осознал, что нашему Open Source HW проекту marsohod.org уже пятнадцать лет. С ума сойти можно. Когда время-то пролетело? Как-то даже не верится. Наверное можно попробовать подвести какие-то итоги.

Ну или можно сделать хоть самому себе отчет о проделанной работе..

Самая дешёвая "оценочная плата" с ПЛИС Xilinx Spartan-6 на AliExpress обойдётся в ровно 3000р.

Здравствуйте. Меня зовут Дмитрий. Данная статья является продолжением статьи Сборка компьютера sap-1 (компьютер Бена Итера) в игре Turing Complete (если вы её не читали то очень советую). Сегодня мы продолжим исследовать блог Бена Итера, но вместо компьютерной игры мы соберем простейшую видеокарту на FPGA чипе.

Привет! В прошлом материале мы поговорили о том, чем серверные видеокарты отличаются от потребительских, а теперь немного углубимся в технические аспекты профессиональных ускорителей и поговорим о решениях, которые доступны (или скоро будут доступны).

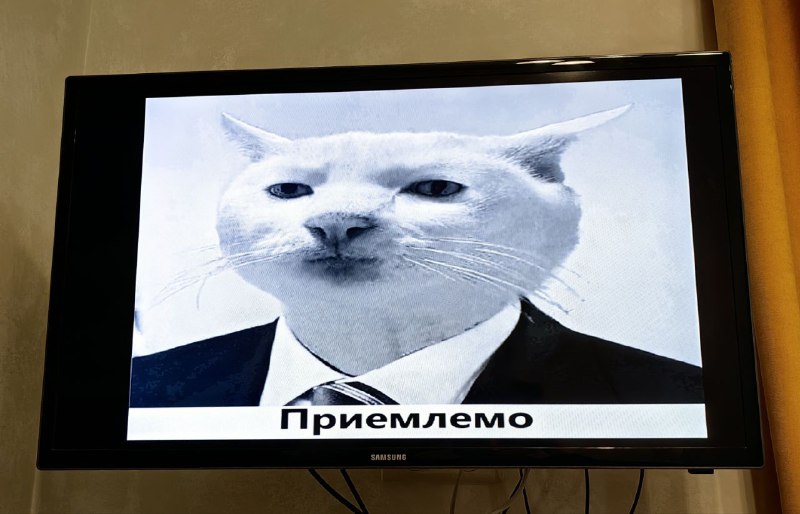

Наверное, каждый второй разработчик на ПЛИС в начале своего пути пытался визуализировать работу своих схем. Кто-то подключал TFT-дисплей, кто-то — VGA монитор. А у меня под рукой оказался только телевизор с композитным входом. Ну что ж, работаем с тем, что есть!

Производительность ARM процессоров каждый год увеличивается и все ближе приближается к x86 процессорам. Компания Apple давно отказалась от процессоров Intel в пользу процессоров собственной разработки на ARM архитектуре. Но домашний/офисный ПК это не только процессор, но и софт, драйвера, и подключение любых устройств из коробки. Компания Shenzhen Xunlong Software вначале 2023 г. выпустила одноплатный компьютер Orange PI 5 Plus на базе высокопроизводительного процессора Rockchip RK3588 с 32 ГБ ОЗУ и возможностью подключения NVMe SSD дисков. По техническим характеристикам такой одноплатный компьютер сопоставим с домашним/офисным ПК. Проверим на сколько комфортно работать за таким одноплатником, смотреть YouTube, видео, и конечно же поиграем, установим Steam от Valve. Но самое главное оценим работу системы «из коробки» т.е. без танцев с бубном. Вначале рассмотрим характеристики Orange PI 5 Plus, затем процессор Rockchip RK3588, установку и настройку системы, подключение периферийных устройств, и посмотрим, на сколько хорош Linux на ARM для домашнего использования. В итоге рассмотрим какие существуют преграды замены текущих x86 систем на ARM.

Читать полностью »