Рубрика «fifo»

Как Работать с UART на Микроконтроллерах ( UART + FIFO = LOG )

2025-12-26 в 19:21, admin, рубрики: cli, DMA, fifo, gpio, printf, shell, uart, Критическая секция, прерыванияЧто Должно Быть в Каждом FirmWare Pепозитории

2022-09-24 в 16:45, admin, рубрики: bsp, C, cli, devops, fifo, Git, make, math, mcu, unit-testing, программирование микроконтроллеров, Производство и разработка электроники, Разработка робототехникиВ этом тексте я предлагаю порассуждать, что же должно быть в нормальном взрослом firmware репозитории (репе/общаке) безотносительно к конкретному проекту. То есть самые универсальные и переносимые программные компоненты (кирпичики), которые могут пригодиться в практически любой сборке.

Загрузчик

Загрузчик нужен для обновления прошивки без специализированного оборудования типа программаторов. Загрузчик обязательно должен уметь обновлять по UART. Остальные интерфейсы обновления по обстоятельствам.

Компонент управления логированием

Мой «Hello World!» на FPGA или очередная версия UART

2018-10-19 в 12:29, admin, рубрики: Altera, diy или сделай сам, fifo, fpga, IP CORE, LPM_ALTPLL, LPM_COUNTER, MEGAFUNCTIONS, PLL, Quartus, rs-232, uart, Verilog, мажоритарный элемент, ПЛИС, Программирование, прототипирование, схемотехника

Наконец-то у меня дошли руки до изучения ПЛИС. А то как-то неправильно получается: драйвера на железо под Linux пишу, микроконтроллеры программирую, схемы читаю (и немного проектирую), надо расти дальше.

Так как мигать светодиодами мне показалось не интересно, то решил сделать простенькую вещь. А именно написать модули приемника и передатчика для UART, объединить их внутри FPGA (заодно понять как использовать IP Core), ну и протестировать это все на реальном железе.

Читать полностью »

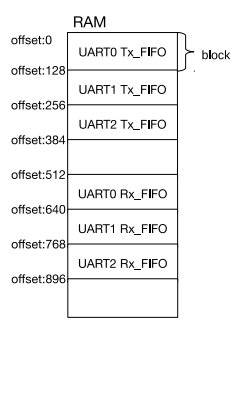

Особенности FIFO буфера UART в ESP32

2018-08-12 в 12:39, admin, рубрики: esp32, fifo, uart, программирование микроконтроллеровУ ESP32 есть три UART-а. Каждый из которых размещает FIFO буфер приемника и FIFO буфер передатчика в общей памяти размером 1024 байта (ESP32 technical reference manual 3.5):

Однако при попытке увеличить размер FIFO буфера передатчика UART2 с 128 до 256 байт получил неожиданный эффект — передаваемые данные портили FIFO буфер приемника UART0, чего согласно документации быть не должно.

FIFO это один из ключевых элементов цифровой техники. Это память типа «первым вошёл-первым ушёл» (first input – first output). Меня как разработчика ПЛИС FIFO окружают повсюду. Собственно я только и делаю что беру данные из одного FIFO и перекладываю в другое. Но как оно работает? В современных САПР конечно уже есть готовые элементы, у Altera есть замечательные мегафункции. У Xilinx есть Core Generator. Но что делать если что-то не устраивает в стандартных решениях? Ответ один – разобраться и написать самому.

Читать полностью »