Внутри каждого современного телефона несколько микросхем ASIС. Ими наполнены автомобили, стойки в центрах обработки данных, датчики «умного дома», и вообще все электронные устройства. Без чипов ASIC был бы невозможен быстрый интернет, трехмерные игры и ускорители машинного обучения.

Рубрика «asic» - 2

ASIC и FPGA: сорок лет эволюции

2023-12-15 в 9:37, admin, рубрики: asic, Electronic Design Automation, fpga, SystemVerilog, Verilog, vhdl, История микроэлектроникиОбзор датчика освещения BH1750

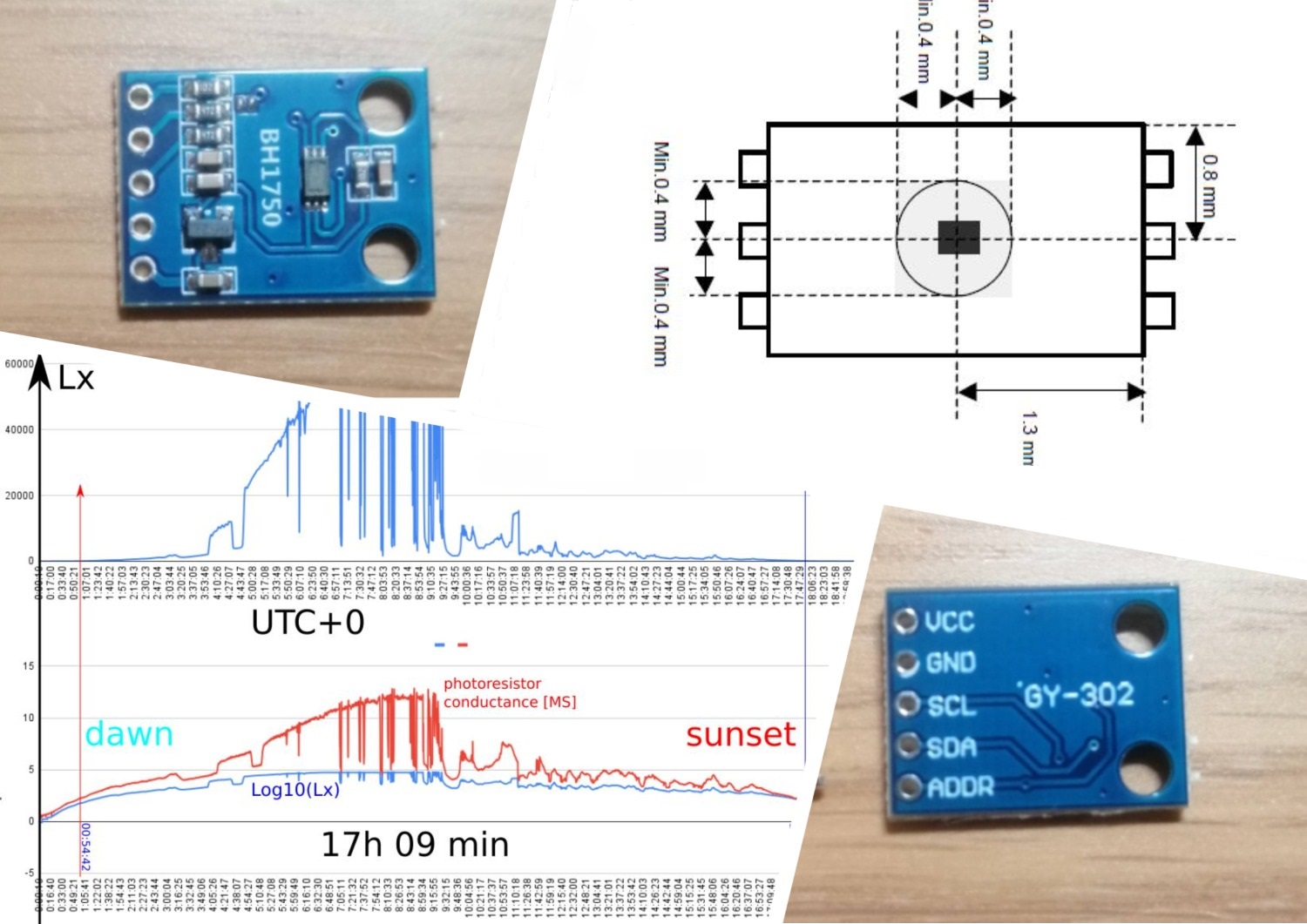

2023-07-15 в 13:33, admin, рубрики: adc, asic, bh1750, diy или сделай сам, I2C, light sensor, Photo diode, rohm, ROHM Semiconductor, датчик освещения, программирование микроконтроллеров, Производство и разработка электроники, фотодиод, Электроника для начинающих

BH1750 это простой цифровой чип датчика освещения с I2C интерфейсом от японской компании Rohm Semiconductor. В этом тексте я представил обзор этого ASIC(а).

Аппаратная часть

Основные технические характеристики

|

Параметр |

Min |

Max |

Unit |

| Читать полностью » |

Первый проект длиною в полтора года…

2023-07-05 в 14:49, admin, рубрики: asic, C#, c++, diy или сделай сам, майнинг, разработка, устройство, Хэш платаКак всё начиналось:

На дворе 2021 год, я занимаюсь ремонтом электроники уже на протяжении десяти лет. Свободное от работы время я посвящаю изучению 3D-моделирования и печати. Для этих целей в 2018 году были куплены два самодельных FDM-принтера.

В один из дней приходит знакомый, держа в руках плату с большим количеством радиаторов. Предлагает посмотреть краем глаза, почему она не работает.

В России всего 2000 проектировщиков чипов. Что с этим делать?

2023-04-11 в 5:41, admin, рубрики: applied materials, asic, fpga, silicon valley, syntacore, Verilog, графика, МИФИ, образование, ПЛИС, программирование микроконтроллеров, Производство и разработка электроники, Школа Синтеза, Электроника для начинающихАппаратные закладки под микроскопом. Обнаружение

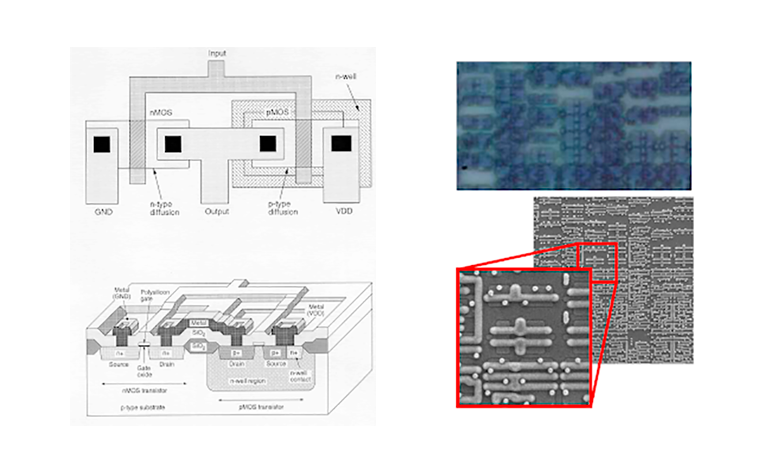

2023-03-27 в 9:00, admin, рубрики: asic, fpga, meltdown, ruvds_статьи, SEM, spectre, Variomill, аппаратные бэкдоры, Блог компании RUVDS.com, закладки, импланты, информационная безопасность, Компьютерное железо, производственный саботаж, Производство и разработка электроники, режим отладки, электрические тесты, Электроника для начинающих, электронный микроскоп

Дисклеймер. Много лет в сообществе технических специалистов идёт дискуссия о возможности внедрения троянов в популярные коммерческие микросхемы. К сожалению, в этот чисто технический вопрос вмешиваются политические аргументы: мол, давайте переходить на российские процессоры, потому что в западных чипах закладки! Такой типичный FUD (см. контрпропаганду на Хабре). Кстати, американские коллеги используют такие же аргументы, но против китайских микрочипов. Похоже, политики любят использовать «пугалки» для принятия выгодных решений, ведь искусство политики древнее самого человечества.

Хотим ещё раз подчеркнуть: мы исследуем эту тему исключительно в общемировом контексте как важную область микроэлектроники и информационной безопасности. А как используют данные факты ангажированные представители индустрии и политики — пусть останется на их совести.

Читать полностью »

Обнаружил баг американской системы образования

2022-11-14 в 6:14, admin, рубрики: asic, CoreMark, cpu, Dhrystone, fpga, Verilog, бенчмарки, курсовой проект, образование, образование за рубежом, программирование микроконтроллеров, Производство и разработка электроники, Процессоры

Обнаружил интересный баг американской системы образования:

У многих студентов в резюме стоит "делал курсовой проект по алгоритму Томасуло, out-of-order суперскаляру, многопоточному процессору итд".

Алгоритм Томасуло как фактор импортозамещения российских процессоров

2022-03-17 в 6:48, admin, рубрики: asic, fpga, syntacore, Verilog, vhdl, алгоритм Томасуло, импортозамещение, микроархитектура процессоров, МИЭТ, программирование микроконтроллеров, Производство и разработка электроники, Процессоры, санкции, суперкомпьютеры

Проектированием простого процессора сейчас никого не удивишь. Любой способный студент может за пару недель написать на верилоге однотактный RISC-V или ARM процессор и синтезировать его для ПЛИС. Процессор будет работать на учебной плате и выполнять простые программы на Си и ассемблере.

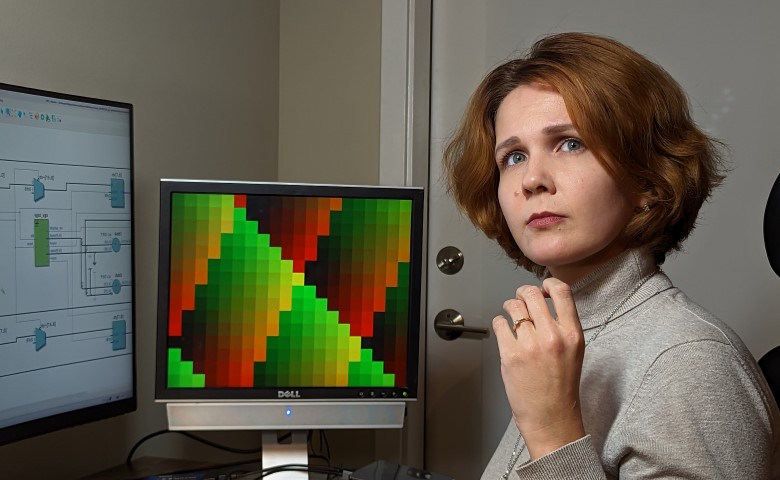

Темное искусство функциональной верификации цифровых микросхем

2022-02-26 в 8:26, admin, рубрики: asic, constraint programming, fpga, functional coverage, simulation, SystemVerilog, verification, Verilog, Алгоритмы, Анализ и проектирование систем, верификация микросхем, математика, Производство и разработка электроники, темпоральная логикаСегодня, в субботу 26 февраля, на Сколковской Школе Синтеза Цифровых Схем Михаил Коробков проводит занятие по технологиям функциональной верификации: constrain solvers, cover bins и concurrent assertions. Примеры, которые мы подготовили для школы, вращаются вокруг протокола AXI для систем на кристалле, вопросы про который спрашивают например на интервью в хардверное отделение компании Meta и другие.

Проектировщики RISC-V из Yadro покажут школьникам как проектировать процессоры

2021-09-07 в 5:50, admin, рубрики: asic, fpga, risc-v, syntacore, Verilog, обработка звука, обучение, параллельное программирование, ПЛИС, программирование микроконтроллеров, Процессоры, сколково, Электроника для начинающих

Через неделю будет выставка ChipEXPO, на которой для будет Читать полностью »

Верификация цифровых схем. Обзор

2019-12-22 в 19:17, admin, рубрики: asic, fpga, systemverilog/vhdl, UVM, verification

Я постараюсь в общем рассказать о верификации цифровых схем.

Верификация в данной области — это важный процесс, требующий привлечения опытных инженеров. Например, специалист по верификации, работающий над системами с ЦПУ, как правило должен владеть скриптовыми языками и языками командных оболочек (Tcl, bash, Makefile и т.п.), языками программирования (С, С++, ассемблер), HDL/HDVL (SystemVerilog [10, Appendix C — история языка][11], Verilog, VHDL), современными методологиями и framework’ами (UVM).

Доля времени, затраченного на верификацию, доходит до 70-80% от всего времени проекта. Одна из основных причин такого внимания в том, что к микросхеме нельзя выпустить “патч” после того, как ее отдали в производство, можно только выпустить “silicon errata” (это не касается проектов ПЛИС/FPGA).

Под цифровыми схемами я подразумеваю:

- сложно-функциональные блоки/intellectual properties (СФБ/IP);

- специализированные заказные микросхемы/application-specific integrated circuit — (ASIC);

- проекты программируемых логических интегральных схем/field-programmable gate — array (ПЛИС/FPGA);

- системы на кристалле/system-on-crystal (СнК/SoC);

- и т.п.