В Киевском Политехническом Институте прошел хакатон нового типа, с одновременной разработкой и программной (Си, ассемблер), и схемотехнической (Verilog) частей системы, синтезируемой для реализации в микросхемы реконфигурируемой логики (ПЛИС/FPGA). Хакатон также поддерживался одной из кафедр Киевского Национального Университета и Imagination Technologies, разработчиком графического процессора PowerVR внутри Apple iPhone. Результат хакатона превзошел ожидания (об этом ниже), и сейчас разрабатываются планы повторить его в других местах, в частности в Томске или Новосибирске.

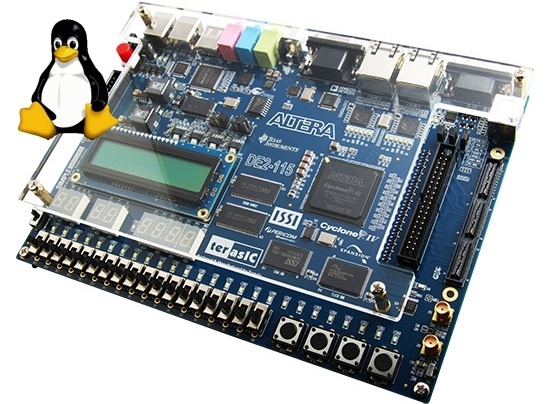

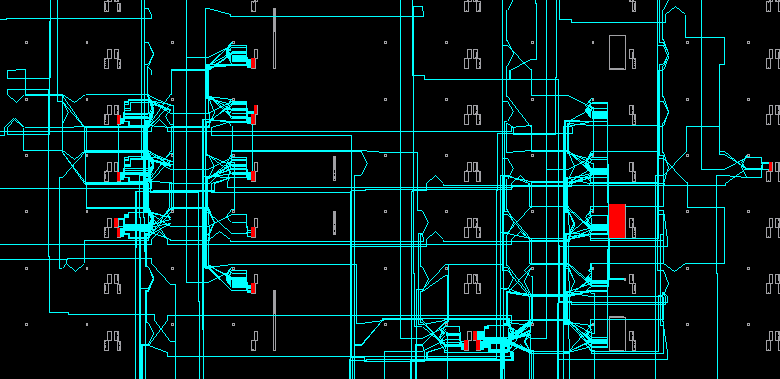

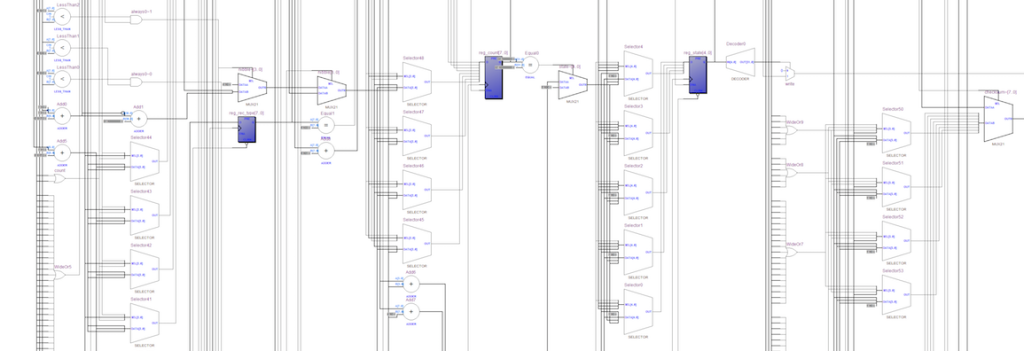

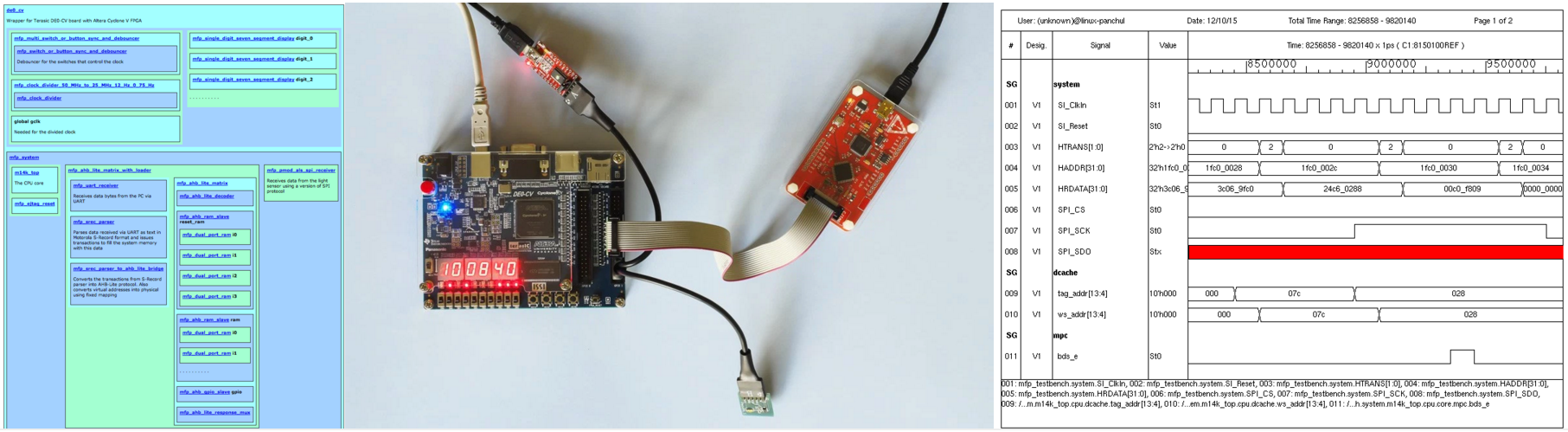

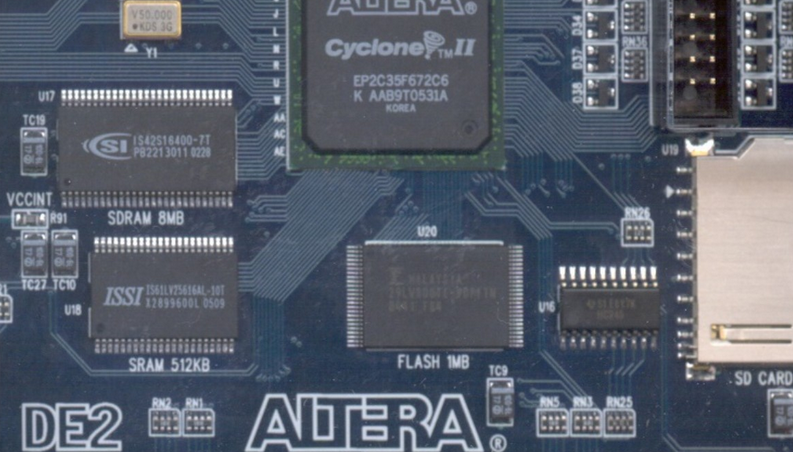

Хакатон в КПИ по MIPSfpga был экспериментальным в том смысле, что обычно в хакатонах участники или просто программируют (например решения SaaS), или делают устройства из готовых фиксированных микросхем и программируют их (Ардуино, STM32 Discovery). Здесь же участники и писали программу, и разрабатывали схему, интерфейсный блок на уровне регистровых передач (Register Transfer Level — RTL), после чего встраивали этот блок в синтезируемую систему с процессорным ядром MIPS microAptiv UP и шиной AHB-Lite, и реализовывали эту систему в FPGA.

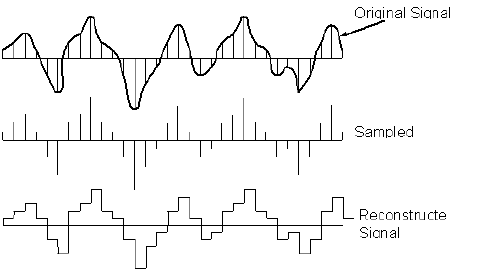

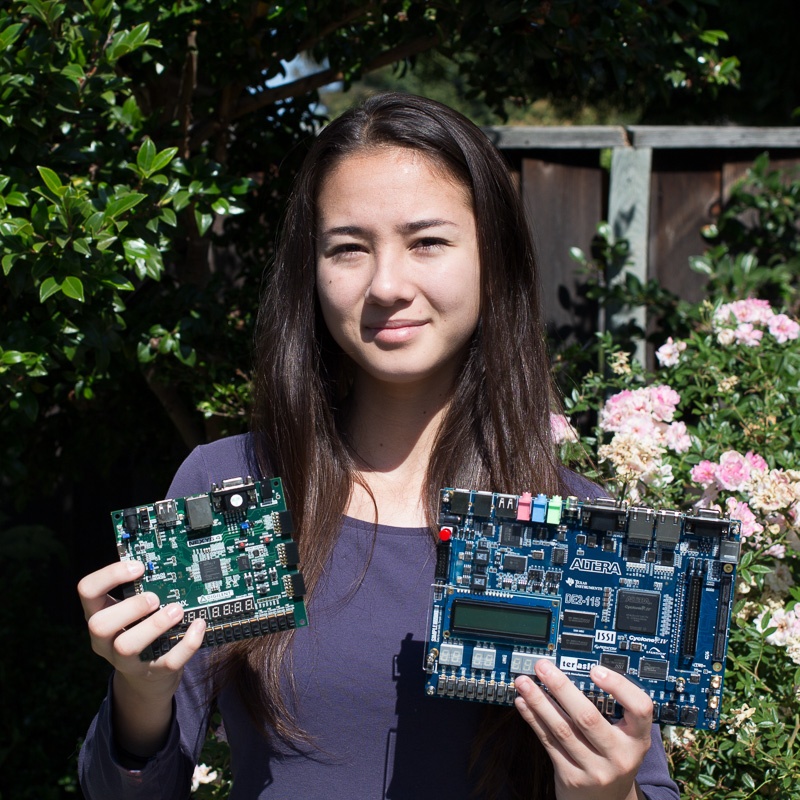

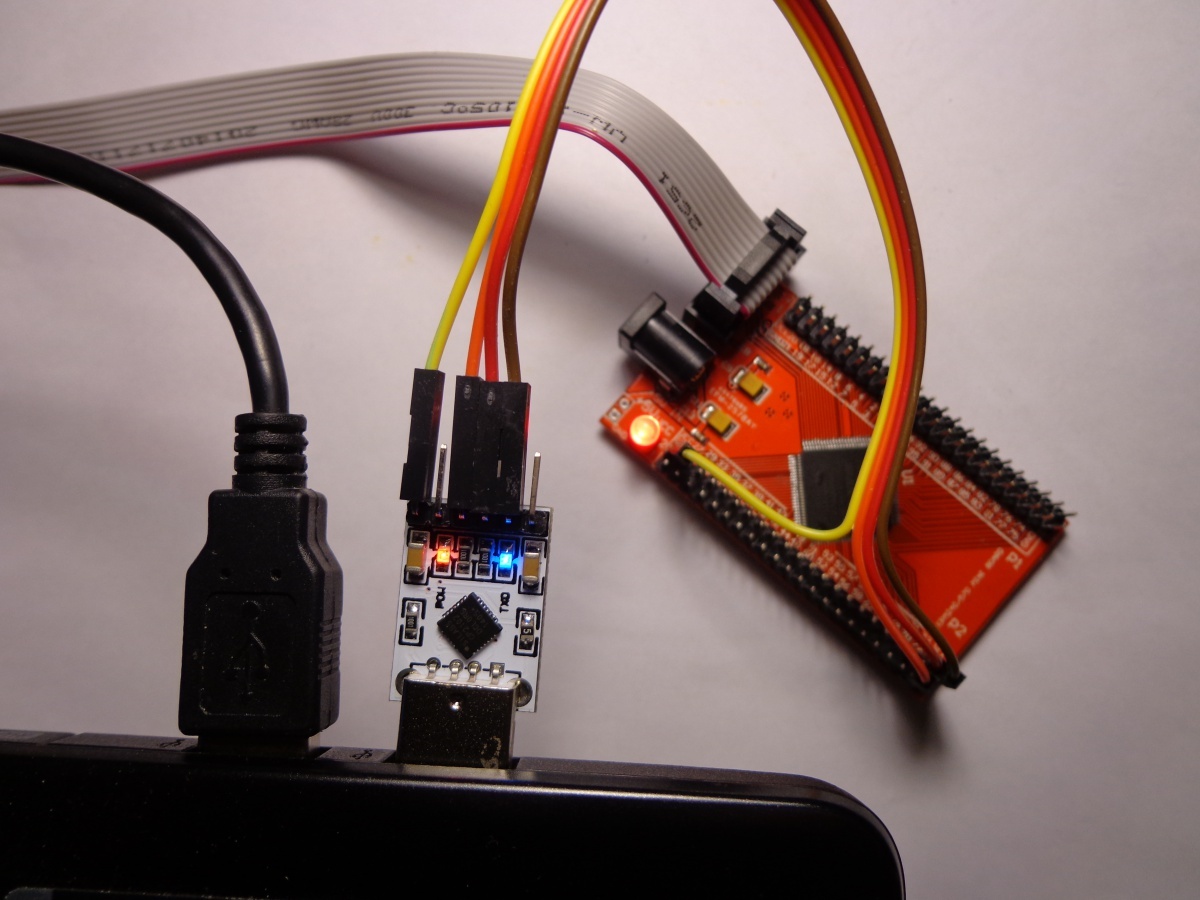

Вот как это выглядело на экранах их ноутбуков, на FPGA-плате и концептуально:

Читать полностью »