Все мы еще с уроков информатики знаем, что информация внутри компьютера передаётся при помощи нулей и единиц, но оказалось, что большинство айтишников, с которыми я общаюсь (и довольно хороших!) слабо представляют, как же, все-таки, устроен компьютер.

Как заставить песок делать то, чего мы от него хотим?

Для большинства людей познания устройства компьютера оканчиваются на уровне его составных элементов — процессор, видеокарта, оперативная память… Но что именно происходит внутри этих чёрных прямоугольничков после подачи питания — магия. В этой статье (скорей всего, даже серии статей) я постараюсь простым языком объяснить, как же устроены эти таинственные прямоугольнички.

Читать полностью »

Рубрика «Altera» - 3

От песка к компьютеру. Часть 1. Атомы и транзисторы

2017-11-23 в 10:58, admin, рубрики: Altera, fpga, intel, vds, vds для обучения, Блог компании VDS.SH, графен, детям, для начинающих, Железо, Научно-популярное, ПЛИС, процессор, транзистор, физика, электроника, Электроника для начинающихЭкскурсия по Музею Истории Компьютеров в Калифорнии, с пользой для разработки. Часть 1. ENIAC, Stretch, CDC6600, IBM-360

2017-09-05 в 7:28, admin, рубрики: Altera, CDC 6600, ENIAC, fpga, IBM 7030, IBM 704, IBM Stretch, IBM System/360 Model 91, IBM/360, Intel FPGA, Lattice, NEAC 2203, NEC SX-3/44, OS/360, silicon valley, SystemVerilog, vhdl, xilinx, алгоритм Томасуло, Алгоритмы, архитектура фон-Немана, высокая производительность, ЕС ЭВМ, калифорния, Киево-Могилянская Академия, Мифический человеко-месяц, МИЭМ НИУ ВШЭ, Новосибирский ТГУ, параллельное программирование, ПЛИС, системное программирование, Фредерик Брукс, Элвис, япония, Япония может сказать NOГоспода! Сегодня мы пройдемся с сибирской девушкой Ириной по Музею истории компьютеров в Маунтин-Вью, Калифорния. Причем пройдемся не как туристы, а для принесения пользы России. Я уже писал в предыдущем посте, что один из эффективных способов для студента изучить проектирование процессоров — это взять какой-нибудь древний, но поучительный процессор, найди документацию по его архитектуре (и какую-нибудь информацию по его микроархитектуре), и спроектировать аналог этого процессора на языке описания аппаратуры SystemVerilog (или VHDL, если он вам больше нравится), после чего реализовать процессор на плате ПЛИС / FPGA (какой именно, не важно — Altera / Intel FPGA, Xilinx или Lattice). В качестве учебника для такого упражнения вы можете начать с Харрис & Харрис, после чего продолжить с книгами для более продвинутой стадии обучения, например Шень-Липасти.

Каким образом все это принесет пользу России? Под такие проекты мы собираемся раздавать FPGA платы на конференции которая пройдет 18-22 сентября в Томске. Туда приедут представители МГУ, МФТИ, МИЭТ, МЦСТ, Imagination Technologies, National Instruments итд. Они будет обсуждать, как обновить программу университетов, чтобы сегодняшние студенты через несколько лет проектировали росийские чипы на уровне передовых западных компаний. Там также будет школа-семинар, на которой будут обсуждать, как делать учебные процессоры — начиная от простейшего schoolMIPS от Станислава Жельнио sparf.

Вот первая фотография из музея в Маунтин-Вью — на ней помимо Ирины и ракеты в центре виден небольшой ящичек. Это бортовой компьютер космической станции «МИР» , который проектировали инженеры советского объединения «ЭЛАС», которое трансформировалось в современную зеленоградскую компанию «ЭЛВИС»:

Итак, темы для учебных проектов — начиная из дремучих десятилетий середины XX века:

Читать полностью »

Взял видеоинтервью у вице-президента Ардуино и обсудил с ней преподавание школьникам ПЛИС-ов – FPGA и языка Verilog

2017-06-06 в 5:13, admin, рубрики: Altera, arduino, artix-7, asic, digilent, fpga, MAX10, open source, Terasic, xilinx, будущее здесь, лшюп, образование, схемотехника, цифровая схемотехника, школьное образование, Электроника для начинающихНа днях я встретился и взял короткое видеоинтервью у Kathy Giori, Vice President Operations Arduino USA. Мы обсудили с Кати новое веяние, которое уже коснулось и Ардуино-коммьюнити: так как программированию микроконтроллеров с помощью Ардуино уже все более-менее научены, то пора делать следующий шаг: учить школьников использовать язык описания аппаратуры Verilog и микросхемы ПЛИС / FPGA, матрицы логических элементов с изменяемыми функциями. А для того, чтобы сделать освоение FPGA проще, стоит воскресить упражнения с микросхемами малой степени интеграции, популярные в 1970-х, в качестве приквела к современным FPGA. Все это закроет брешь между физикой и программированием, дискретными элементами и микроконтроллерами, транзистором и Ардуино.

FPGA и платы можно использовать от любого производителя (Xilinx, Altera, Lattice, Digilent, Terasic), все что я пишу ниже, не имеет привязки к той или иной компании.

В разговоре с Кати принимала участие преподаватель Стенфорда Светлана Хутка, которая рассказала Кати об эксперименте по бесплатному обучению школьников использованию FPGA в Киеве, силами преподавателей-энтузиатов из нескольких киевских вузов. После этого я поделился с Кати планами проведения следующего такого эксперимента на известной еще с советских времен летней школе юных программистов в Новосибирске, а также поговорил с другими присутствующими товарищами из Ардуино-коммьюнити о внедрении FPGA в двух школах и одном коледже Silicon Valley.

Портирование MIPSfpga на другие платы и интеграция периферии в систему. Часть 3

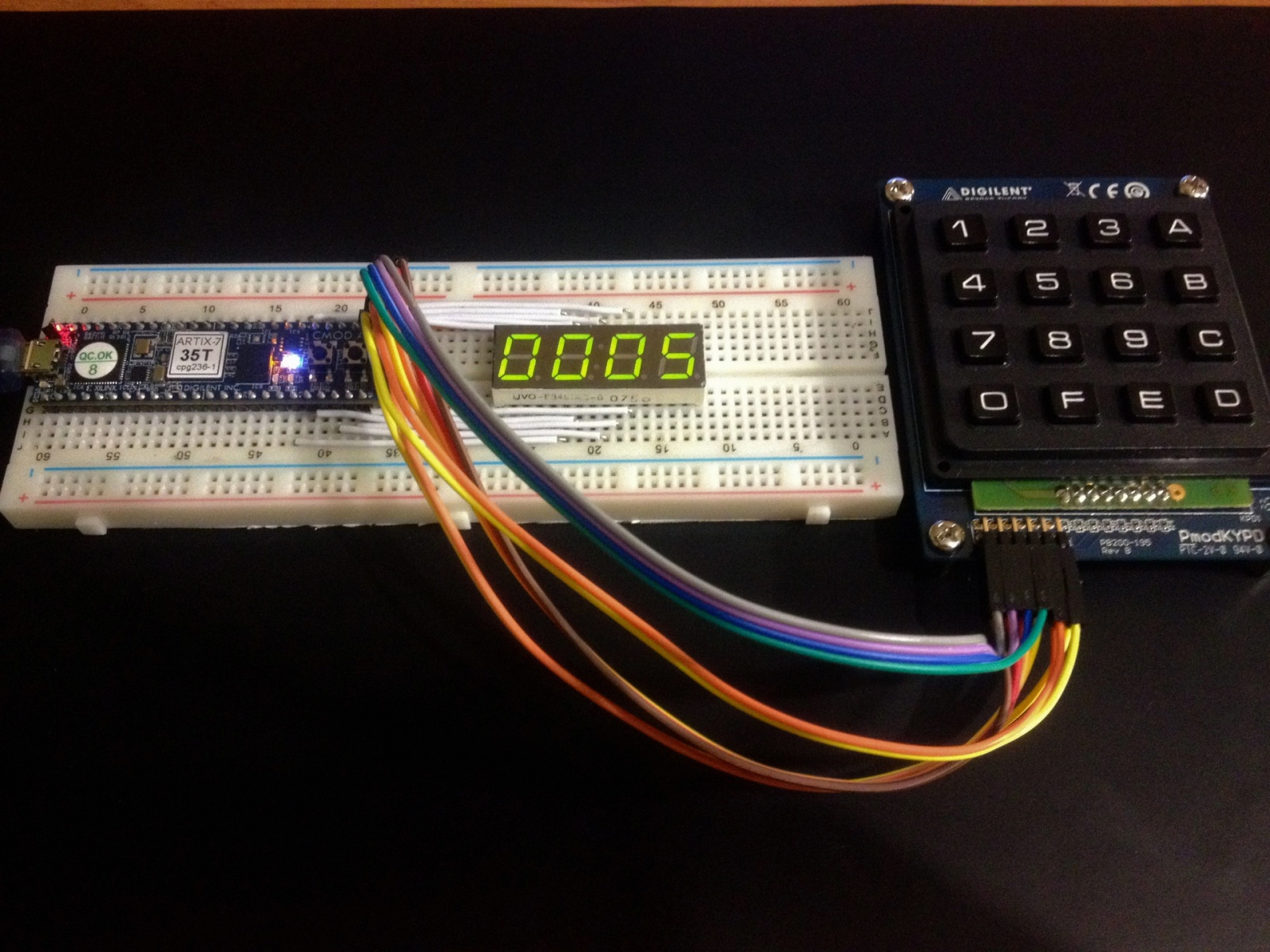

2017-05-31 в 3:55, admin, рубрики: Altera, fpga, imagination technologies, mips, MIPS microAptiv UP, MIPSfpga, SPI, uart, Verilog, vhdl, xilinx, Анализ и проектирование систем, параллельное программирование, ПЛИС, программирование микроконтроллеровВ первой части я описал на примере cmoda7 как портировать MIPSfpga (Портирование MIPSfpga на другие платы и интеграция периферии в систему. Часть 1) на FPGA платы отличные от уже портированых среди которых такие популярные как: basys3, nexys4, nexys4_ddr фирмы Xilinx, а так же de0, de0_cv, de0_nano, de1, DE1, de10_lite, de2_115, DE2-115 фирмы Altera(Intel), во второй части как интегрировать клавиатуру Pmod KYPD (Портирование MIPSfpga на другие платы и интеграция периферии в систему. Часть 2).

В этой части добавим к MIPSfpga-plus встроенный АЦП, и популярный LCD от Nokia 5100.

С предыдущих частей можно сделать вывод, что интеграция периферии в MIPSFPGA состоит из пять основных этапов:

- Добавление модуля интерфейса общения с периферией (i2c, spi, и т.д.).

- Соединение входных/выходных портов модуля с шиной AHB-Lite.

- Присваивание адресов сигналов подключаемого устройства.

- Добавление констрейнов на физические контакты платы.

- Написание программы для MIPS процессора.

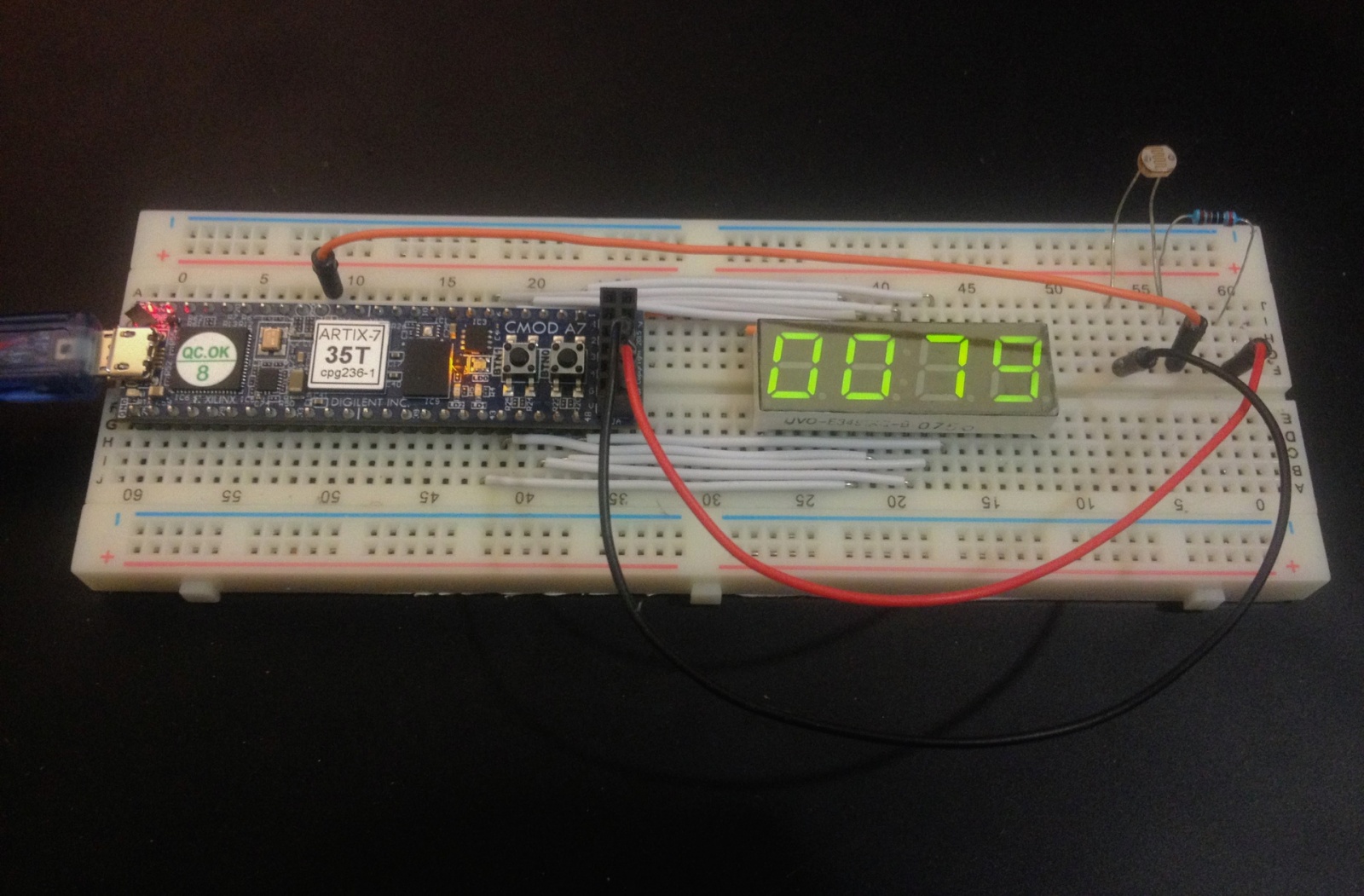

Подключение встроенного в cmoda7 АЦП

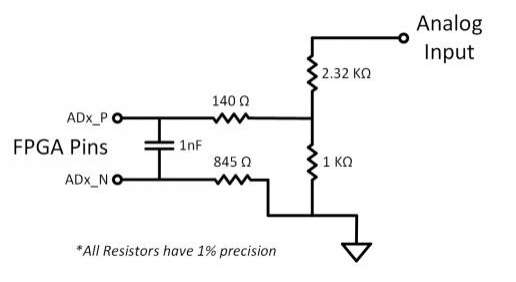

Как я уже говорил плата cmodA7 имеет встроенный АЦП, pin 15 и 16 используются в качестве аналоговых входов модуля FPGA. Диапазон работы встроенного АЦП от 0-1V, поэтому используется внешняя схема для увеличения входного напряжения до 3.3V.

Эта схема позволяет модулю XACD точно измерить любое напряжение от 0 В и 3,3 В (по отношению к GND). Чтобы работать с АЦП в Vivado существует блок IP (интеллектуальной собственности) Xilinx, с помощью которого можно будет просто его интегрировать в нашу систему MIPSfpga.

Читать полностью »

Портирование MIPSfpga на другие платы и интеграция периферии в систему. Часть 2

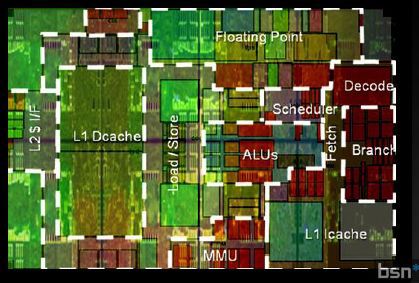

2017-05-31 в 3:39, admin, рубрики: Altera, fpga, imagination technologies, mips, MIPS microAptiv UP, MIPSfpga, SPI, uart, Verilog, vhdl, xilinx, Анализ и проектирование систем, ПЛИС, программирование микроконтроллеровMIPSfpga микропроцессор MIPS32 microAptiv описаный на языке Verilog для образовательных целей фирмы Imagination, который имеет кэш-память и блок управления памятью. Код процессора доступен пользователю (инструкция по скачиванию) и может использоваться для моделирования и реализации процессора на FPGA плате.

Данная статья является продолжением статьи о том как портировать MIPSfpga-plus на другие платы, и в ней будет описано как интегрировать периферию в систему MIPSfpga:

Так же о том как начать работать с MIPSfpga написано в статье:

habrahabr.ru/post/275215

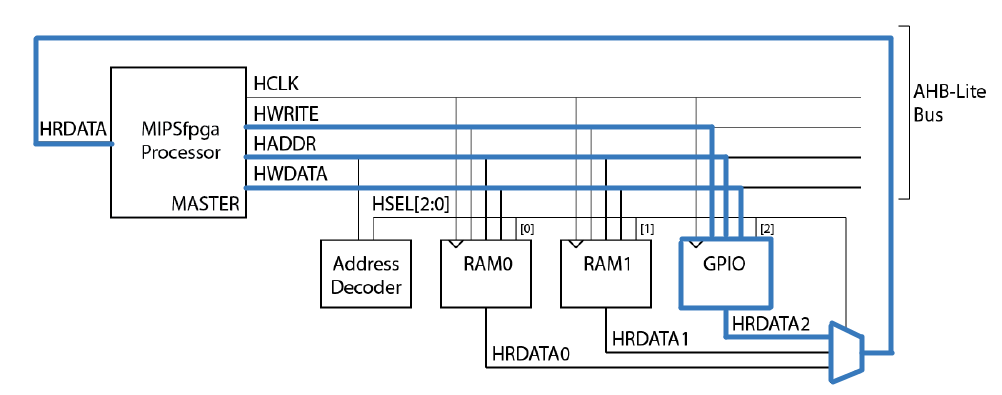

Процессор использует интерфейс памяти для связи с периферийными устройствами. То есть, это означает что данные записываются и считываются с подключенной периферии так же, как и с блока памяти RAM. Интеграция периферии в процессор осуществляется подключением к шине AHB-Lite(подробная документация). Подробней попробуем разобраться в процессе подключения.

Для начала нужно иметь понятие как будут проходить сигналы по шине AHB-Lite:

Видно, что процесс считывания данных с периферии осуществляется по сигналу HRDATA, передача данных производится по HWRITE с активным высоким уровнем на сигнале разрешения записи, выбор GPIO осуществляется выбором адреса на HADDR.

Читать полностью »

Портирование MIPSfpga на другие платы и интеграция периферии в систему. Часть 1

2017-05-30 в 13:19, admin, рубрики: Altera, fpga, imagination technologies, mips, MIPS microAptiv UP, MIPSfpga, SPI, uart, Verilog, vhdl, xilinx, Анализ и проектирование систем, ПЛИС, программирование микроконтроллеровMIPSfpga представляет собой предназначенный для образовательных целей микропроцессор MIPS32 microAptiv фирмы Imagination, который имеет кэш-память и блок управления памятью. Код процессора на языке Verilog доступен пользователю и может использоваться для моделирования и реализации процессора на FPGA плате.

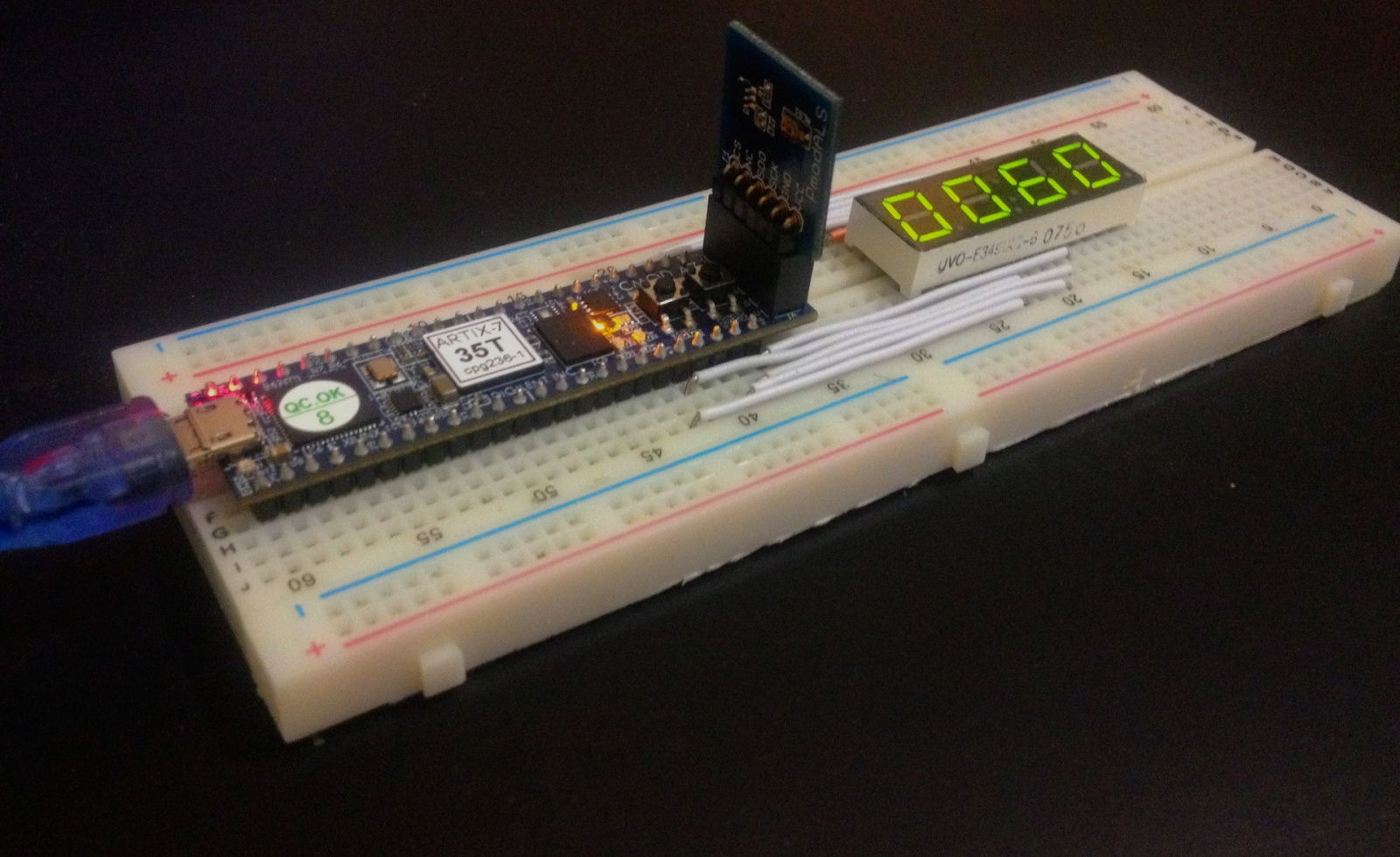

В даной статье будет описано на примере Digilent cmodA7 как портировать процессор MIPSfpga-plus на другие платы.

На сегодняшний день MIPSFPGA портирован на популярные платы таких фирм как ALTERA и Xilinx, среди них Basys 3, Nexys4 ddr, и другие (полный список находится на github). Такие платы наиболее популярны среди разработчиков на FPGA. Цена на такие платы довольно не маленькая, да и загружаются программы в ядро MIPSfpga с использованием интерфейса EJTAG и адаптера Bus Blaster ценой около 50$. Адаптер Bus Blaster получает команды по высокоскоростному кабелю USB 2.0 и преобразует их в последовательный протокол EJTAG, это позволяет загружать программы в ядро MIPSfpga и управлять отладкой программ, которые на нем выполняются. Проблема с относительно дорогим Bus Blaster была решена введением в систему MIPSfpga ряда улучшений. Улучшеный вариант системи MIPSfpga, названый MIPSfpga-plus включает в себя такие новые функции:

— Возможность загрузки программного обеспечения с использованием USB-to-UART коннектора ценой в $ 5 FTDI вместо $ 50 Bus Blaster, который иногда не так уж и легко достать.

— Возможность изменять тактовую частоту на лету с 50 или 25 МГц до 1 Гц (один цикл в секунду) для наблюдения за работой процессора в режиме реального времени, включая промахи в кэш-памяти и перенаправления конвеера.

— Пример интеграции датчика освещенности с протоколом SPI.

— Небольшая последовательность инициализации программного обеспечения, которая вписывается в 1 КБ вместо 32 КБ памяти, что позволяет переносить MIPSfpga на более широкий выбор плат FPGA без использования внешней памяти. Реализация UART описана в статье: MIPSfpga и UART.

Читать полностью »

Расчет корректирующего КИХ-фильтра на ПЛИС

2017-03-28 в 12:40, admin, рубрики: Altera, CIC, dsp, FIR, fpga, github, math, Matlab, octave, opensourse, xilinx, математика, обработка изображений, программирование микроконтроллеров, Разработка систем передачи данных

Всем привет! Написать эту статью меня побудило выступление на семинарах по цифровой обработке сигналов, где слушатели всегда заостряли интерес к методике вычисления корректирующих FIR-фильтров, несмотря на то, что эту тему я затрагивал поверхностно и по большей части рассказывал об этом в ознакомительных чертах. Если публика желает получить тайные знания, то почему бы ими не поделиться. В этой статье я постараюсь в доступной форме изложить алгоритм расчета корректирующих КИХ фильтров, который необходим для выравнивания АЧХ в полосе пропускания после звеньев CIC фильтров в задачах децимации и интерполяции сигналов. В частности, рассмотрим проектирование фильтров на современных ПЛИС Xilinx. Как обычно, в конце статьи будет ссылка на полезные скрипты для расчета различных фильтров и получение файла коэффициентов фильтра-корректора.

Предполагается, что читатель знаком с основами цифровой обработки сигналов и имеет представление о CIC и FIR фильтрах. Приступим.

Читать полностью »

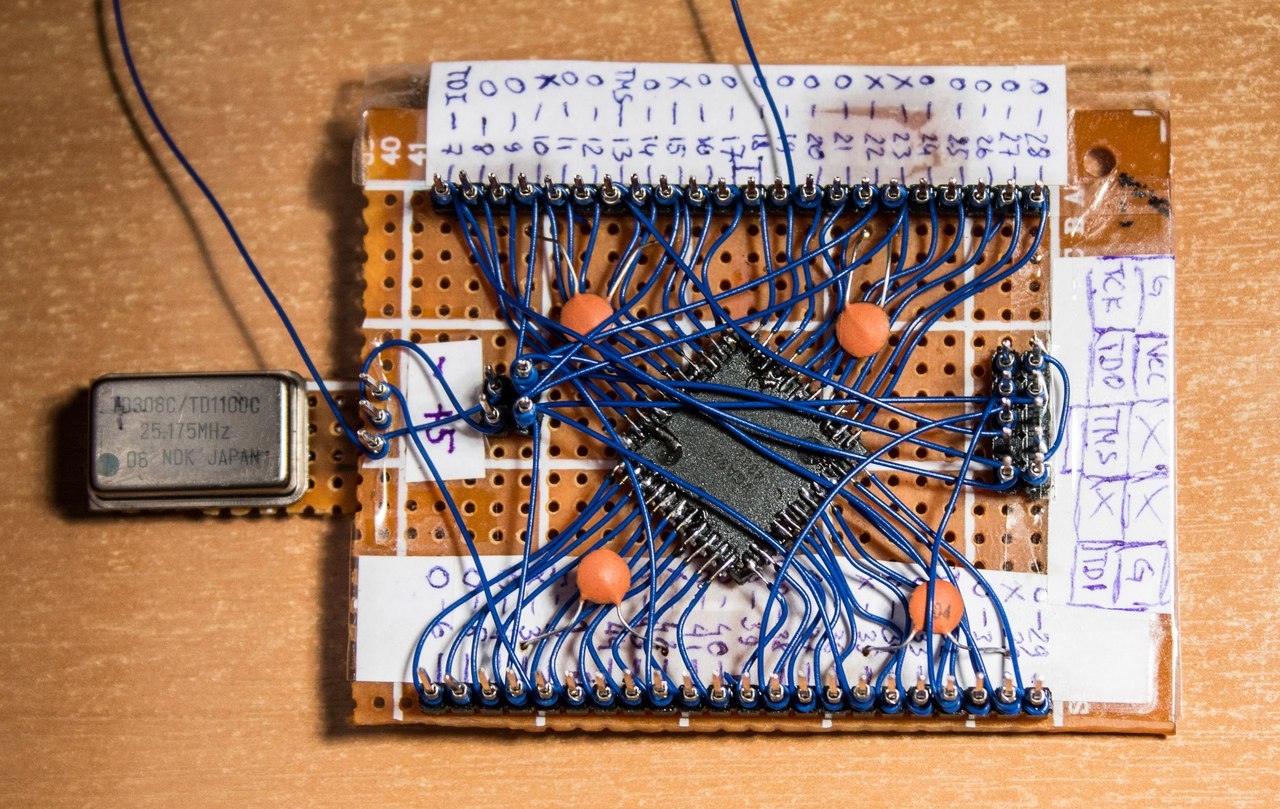

Отладочная плата ПЛИС — Франкенштейн. Звуки и музыка

2016-12-28 в 7:24, admin, рубрики: Altera, fpga, Verilog, ПЛИС, Программирование, программирование микроконтроллеров, сигнализация, сиренаСегодня у нас самая предновогодняя серия про ПЛИС и отладочную плату Френки. Предыдущие серии 1, 2.

Мы уже передавали тоновые сигналы по радио с помощью нашей платы Франкенштейн. Теперь попробуем воспроизводить звуки и музыку.

Мы уже передавали тоновые сигналы по радио с помощью нашей платы Франкенштейн. Теперь попробуем воспроизводить звуки и музыку.

Для этого подключим к ПЛИС обычный динамик. К Френки подключен генератор на 25.175 МГц. Если поделить эту частоту до диапазона слышимых частот и подать на вывод ПЛИС, то мы можем услышать звук. Меня частоту мы можем получить разные звуки.

Тестировать качество звучания будет самый лучший слухач в доме — Маша. Диапазон частот в 60 КГц — это вам не шутки! )))

Отладочная плата ПЛИС — Франкенштейн. Часы. Altera EPM7064 VS Lattice LC4064v

2016-12-27 в 6:46, admin, рубрики: Altera, fpga, Lattice, Verilog, ПЛИС, Программирование, программирование микроконтроллеров, ЧасыПродолжение предновогодней серии приключений маленькой ПЛИС Altera EPM7064 на отладочной плате — Франкенштейн. В предыдущей серии...

Настала пора сравнить две ПЛИС из одной весовой категории: Altera EPM7064 и Lattice LC4064v. Хотя, один у них — только вес — это 64 макроячейки. В остальном, судя по параметрам, у этих ПЛИС совсем разные назначения. ПЛИС от Altera, судя по документации 2005 года, является просто не молодой, от этого и обладает низким количеством ячеек. Так же, обладает популярным по тем временам напряжением питания — 5 вольт. Максимальная рабочая частота не превышает 200 МГц. В то же время Lattice может работать до частот в 400 МГц, но при этом, питается от напряжения — 3.3 вольта. Да, это не так удобно, как 5 вольт, если мы хотим взаимодействовать со старыми схемами (однако, заявлена толерантность к 5В). В документации на Lattice этой серии указан 2014 год, поэтому я предположу, что это современные высокоскоростные ПЛИС, но малого объема, и судя по "SuperFAST CPLD" в описании, позиционируются они несколько иначе.

Настала пора сравнить две ПЛИС из одной весовой категории: Altera EPM7064 и Lattice LC4064v. Хотя, один у них — только вес — это 64 макроячейки. В остальном, судя по параметрам, у этих ПЛИС совсем разные назначения. ПЛИС от Altera, судя по документации 2005 года, является просто не молодой, от этого и обладает низким количеством ячеек. Так же, обладает популярным по тем временам напряжением питания — 5 вольт. Максимальная рабочая частота не превышает 200 МГц. В то же время Lattice может работать до частот в 400 МГц, но при этом, питается от напряжения — 3.3 вольта. Да, это не так удобно, как 5 вольт, если мы хотим взаимодействовать со старыми схемами (однако, заявлена толерантность к 5В). В документации на Lattice этой серии указан 2014 год, поэтому я предположу, что это современные высокоскоростные ПЛИС, но малого объема, и судя по "SuperFAST CPLD" в описании, позиционируются они несколько иначе.

Как нам их сравнить? Попробуем решить на них одну и ту же задачу. Часы на Lattice LC4064v мы уже попробовали сделать и у нас получилось. Теперь попробуем сделать часы на Altera EPM7064 — на нашем Франкенштейне.

Отладочная плата ПЛИС — Франкенштейн. Телеграфный передатчик

2016-12-26 в 7:04, admin, рубрики: Altera, fpga, Verilog, передатчик, ПЛИС, Программирование, программирование микроконтроллеровБегут последние деньки уходящего года. Предновогодняя суета. А для тех, у кого выдалась свободная минутка на работе, я предлагаю серию статей про самодельную отладочную плату на базе ПЛИС Altera EPM 7064.

Недавно мне потребовалось найти пару 1U корпусов под мой проект. И в качестве альтернативы новым, мы решили поискать старые приборы в 1U формате, внутренности выкинуть, а корпус использовать по назначению. Но, открыв корпус, я был в шоке! Целых четыре ПЛИС от Altera, да к тому же 5 вольтовых. Я не смог удержаться, чтобы одну из них не попробовать в деле!

Паяльной станции у меня нет, ЛУТ технологию я не практикую. Поэтому я взял строительный фен на 250 градусов и отковырял микросхему ПЛИС от платы. Переходной платы для такого корпуса у меня тоже не было, поэтому я взял обычную макетку, впаял в нее стойки и с помощью накрутки и пайки, соединил выводы микросхемы со стойками. Вывел разъем JTAG и питания, прикрутил генератор. Это все, что нужно для начала работы с микросхемой

Что можно сделать из такой маленькой ПЛИС? Радиолюбители решают такую проблему очень просто: в любой непонятной ситуации мы делаем передатчики! Из чего? Да из чего угодно, что под руку попало в данный момент! А сегодня у нас Altera EPM7064.

Читать полностью »