Рубрика «Altera»

Образовательные технологии опробованные в России — работают и в США

2025-10-29 в 16:01, admin, рубрики: Altera, asic, Cal Poly, fpga, Gowin, SystemVerilog, TinyTapeout, Verilog, vlsi, xilinxOSHW проекту marsohod.org 15 лет

2025-04-15 в 6:44, admin, рубрики: Altera, fpga, Gowin, марсоход, сезон open source

Совсем недавно осознал, что нашему Open Source HW проекту marsohod.org уже пятнадцать лет. С ума сойти можно. Когда время-то пролетело? Как-то даже не верится. Наверное можно попробовать подвести какие-то итоги.

Ну или можно сделать хоть самому себе отчет о проделанной работе..

Made at Intel. Acquisitions -3

2023-03-19 в 11:39, admin, рубрики: Altera, amd, intel, mcafee, xilinx, Читальный залСегодня у нас на очереди третья заключительная часть повествования о приобретениях Интел. (начало – здесь и здесь). Я сразу оговаривался о том, что вряд ли смогу осветить всю M&A активность, поэтому сфокусируюсь на наиболее знаковых и памятных событиях за 22 года моей работы в компании. Начнем,пожалуй, с Альтеры.

Altera

Как прошла ПЛИСовая конференция в Питере?

2022-01-17 в 15:49, admin, рубрики: Altera, community, developers, fpga, Intel FPGA, xilinx, высокая производительность, конференции, ПЛИС, Производство и разработка электроникиПрошло всё отлично, 35 человек собралось, 7 докладов выслушано, 12 человек осталось на афтерпати.

Следующее мероприятие пройдет в Москве, Минске, Томске и Санкт-Петербурге в апреле-мае, подробности тут.

Все материалы собраны в отдельные плейлисты - встреча в Москве // слёт в Санкт-Петербурге, под каждым из видео ссылка на презентацию докладчика.

Как разработать микросхему, от идеи до результата. Часть 2. Установка программного обеспечения

2021-12-08 в 9:00, admin, рубрики: Altera, arduino, avr, c++, fpga, ic design, intel, IoT, mips, MIPSfpga, ruvds_статьи, stm32, SystemVerilog, Verilog, vhdl, vlsi design, xilinx, Блог компании RUVDS.com, микроконтроллеры, микросхемы, ПЛИС, программирование микроконтроллеров, Производство и разработка электроникиНапоминаю, что я продолжаю идти к цели — сделать свой собственный Отечественный Процессор (TM). Продолжение процесса разработки можно посмотреть под катом.

INTEL (Altera) USB Byte Blaster на STM32

2020-12-22 в 8:30, admin, рубрики: Altera, cpld, fpga, intel, stm32, USB BYTE BLASTER, Алгоритмы, Производство и разработка электроникиЗачастую если в устройстве есть программируемая логика, присутствует и процессор/микроконтроллер.

В какой-то момент мне надоело разводить на платах разъем JTAG, он занимает много места на плате и по сути нужен только для разработки. В конечном устройстве он вообще без надобности.

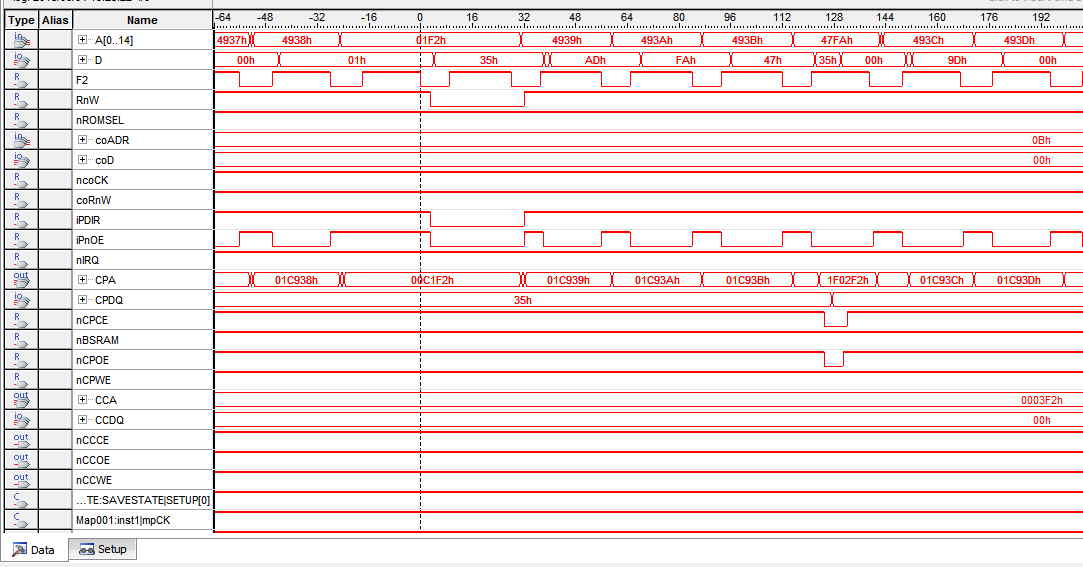

Очень часто для проверки правильности реализации Verilog кода или вообще "посмотреть как сигнальчики бегают" я использую SignalTap II Logic Analyzer, штука удобная и наглядная, я думаю многие сразу узнают по изображению:

Расчет временных ограничений для ПЛИС простым языком

2020-07-16 в 10:23, admin, рубрики: Altera, constraints, fpga, RTL, slackЗдравствуйте. Эта статья написана для самых-самых новичков в мире ПЛИС. В ней я попытаюсь максимально просто и понятно рассказать что такое временны́е ограничения (timing constraints), накладываемые на проекты под ПЛИС.

Статья создана на основе собственного опыта попыток объяснить тему самому себе, студентам-практикантам и любопытным коллегам так, чтобы не погружаться в заумные академические дебри, а максимально просто, прозрачно, на пальцах. Я учился работать с ПЛИС без учебы и подготовки по этой теме и знаю по своему опыту как трудно что-то понять не имея теоретического базиса в этой теме и в схемотехнике. Если на данную статью наткнется некий мэтр и воскликнет, что описанное — элементарно, то посмею не согласиться. Для какого-нибудь студента четвертого курса статья будет полезной и поможет разобраться во всех этих слэках, сетапах и холдах.

Читать полностью »

Building a Bare-Metal Application on Intel Cyclone V for Absolute Beginners

2019-08-17 в 17:07, admin, рубрики: Altera, Cyclone V, cyclone v soc, fpga, intel, программирование микроконтроллеровSetting up Linux on the development board like SocKit with a double-core ARM Cortex A9 is not rocket science. A manufacturer of the board supports the ready-to-use image, appropriate for installing on SD card or another media. But what if you are craving to touch bare metal, approaching a neck-breaking speed of code not restrained by an OS core? Well, it is possible, but not so easy and obvious. In this short essay, I'll give you step-by-step instruction, how to build and run you first bare-metal application on Cyclone V SoC, that uses ARM Cortex A9 core of the HPS subsystem of the SoC.

You need to have the development board with Intel (Altera) Cyclone V SoC. I used SoCKit board: