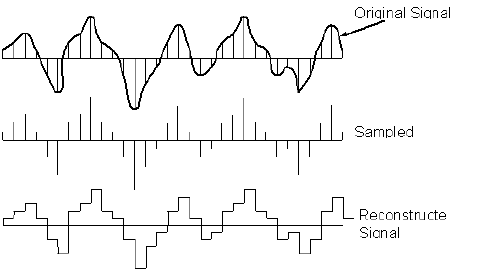

Всем привет! В данной статье речь пойдет о подключении микросхем АЦП к кристаллам ПЛИС. Будут рассмотрены основные особенности соединения узлов схем, представлены современные АЦП и их характеристики. В статье будут даны практические советы по быстрому и правильному подключению АЦП к ПЛИС с минимальными временными затратами. Кроме того, речь пойдет о принципах подключения тех или иных АЦП, будет рассмотрен входной буфер ПЛИС и его базовые компоненты – триггеры, узлы задержки IODELAY, сериализаторы ISERDES и т.д. Более детально с примерами программного кода на языке VHDL будет проведен обзор основных элементов, требуемых для качественного приёма данных от АЦП. Это входной буфер, узел упаковки данных для одноканальных и многоканальных систем, модуль синхронизации и передачи данных на базе FIFO, узел программирования АЦП по интерфейсу SPI, узел синтеза частоты данных – MMCM/PLL. Также в статье будет представлен обзор законченных устройств (в стандарте FMC) от ведущих зарубежных и отечественных производителей аналоговых и цифровых схем. В конце статьи вы найдете ссылку на исходные коды универсального узла приёмника данных от многоканальных схем АЦП. Код простой и гибкий в конфигурировании, он представлен на языке VHDL и заточен на микросхемы ПЛИС Xilinx 7 серии и выше, но может быть применен и в других кристаллах ПЛИС.

Читать полностью »