Мы уже смирились с тем, что рост тактовой частоты процессоров остановился и производители пошли по пути распараллеливания вычислений. Однако и число ядер типичного процессора общего назначения, быстро одолев отметки 2 и 4, остановилось в районе 8. Некоторые даже собрались хоронить закон Мура.

Мы уже смирились с тем, что рост тактовой частоты процессоров остановился и производители пошли по пути распараллеливания вычислений. Однако и число ядер типичного процессора общего назначения, быстро одолев отметки 2 и 4, остановилось в районе 8. Некоторые даже собрались хоронить закон Мура.

У такого застоя есть объективная причина. Если разница между 2, 4 или 8 ядрами скорее количественная, то уже 16-ядерный процессор сталкивается с принципиальными ограничениями традиционной архитектуры. Дело в том, что на протяжении последних нескольких десятилетий основой коммуникации между отдельными IP-блоками чипа служила шина. Пока блоков было немного, она справлялась, но когда начали плодиться ядра, эта архитектура исчерпала себя. Шина представляет собой общую среду передачи данных, к которой подключено несколько блоков процессора. В каждый момент времени один блок может передавать данные, а все остальные — получать. Если нескольким блокам нужно передавать одновременно — возникает коллизия, а значит и задержка. При числе ядер больше восьми задержки становятся неприемлемо большими, практически полностью перечёркивая преимущества параллельной работы нескольких ядер.

Число ядер можно увеличить ещё немного, разделив шину на несколько сегментов, объединённых мостами, однако это скорее «костыль», который плохо масштабируется и не решает основную проблему. Настоящее решение, которое позволит объединять сотни блоков на одном чипе — это хорошо известная всем сеть с коммутацией пакетов, или Network on Chip.

Переход от шины к сети вполне закономерен. Именно так развивались телекоммуникационые сети: радиоэфир — типичная «шина», телефонные сети — коммутация каналов с помощью матричных коммутаторов, интернет — коммутация пакетов. Так же развивалась и компьютерная периферия — современная шина PCI Express на самом деле вовсе не шина, а сеть c топологией типа звезда. Так же развиваются и процессоры — сначала прямые соединения между блоками, затем шины и матричные коммутаторы и, наконец, сети.

Переход от шины к сети вполне закономерен. Именно так развивались телекоммуникационые сети: радиоэфир — типичная «шина», телефонные сети — коммутация каналов с помощью матричных коммутаторов, интернет — коммутация пакетов. Так же развивалась и компьютерная периферия — современная шина PCI Express на самом деле вовсе не шина, а сеть c топологией типа звезда. Так же развиваются и процессоры — сначала прямые соединения между блоками, затем шины и матричные коммутаторы и, наконец, сети.

В архитектуре NoC каждое ядро или блок процессора соединён с маршрутизатором, через который происходит его общение с другими блоками. Сами маршрутизаторы объединены в сеть, по которой пакеты данных путешествуют от одного блока к другому, так же как пакеты в обычной компьютерной сети. Это значительно упрощает топологию микросхемы и снимает ограничения по масштабированию — в отличие от шины, множество блоков способно общаться одновременно, не мешая друг другу. Компьютерное моделирование и опытные образцы многоядерных процессоров показывают, что при большом количестве ядер такая архитектура превосходит традиционную по многим показателям.

Естественно, напрямую перенести логику и протоколы работы интернета внутрь чипа было бы неразумно и неэффективно. Здесь совсем другие технологические ограничения и задачи:

- Очень жёсткие требования к задержкам и энергопотреблению. Коммутаторы должны работать с наносекундными задержками и быть очень экономичными. Расходы энергии на передачу данных между блоками составляют значительную часть общего потребления современных чипов.

- Простота и минимализм. Коммутаторы на чипе должны занимать мало места, а значит не могут иметь сложную логику и большой размер буфера.

- Параллельное, а не последовательное соединение. На физическом уровне внутри чипа выгоднее предавать биты не последовательно по одному проводнику, а по 32 или 64 параллельным каналам.

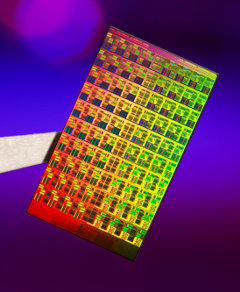

Исследованиями NoC занимаются ведущие компании и университеты мира. Так, в 2007 году Intel разработала экспериментальный процессор c 80-ю ядрами и производительностью 1 терафлопс при энергопотреблении всего в 62 ватта. В 2010 был представлен 48-ядерный «Облачный компьютер на кристалле» (Single chip cloud computer).

В апреле этого года была опубликована работа группы ученых MIT, которые создали прототип 16-ядерного процессора, в котором были применены специфические для NoC-систем оптимизации — виртуальный обход (virtual bypassing) и сигналы с малой амплитудой (low-swing signaling). Эти технологии позволили приблизиться к теоретическим пределам пропускной способности и задержек и заметно снизить энергопотребление.

Как они работают? Обычный маршрутизатор сохраняет полученный пакет в буфер, анализирует его заголовок и решает, куда его отправить дальше. Virtual bypassing позволяет передать пакет практически без задержек, за счёт того, что заголовок посылается заранее, и коммутатор успевает сделать нужные переключения цепей к тому моменту, как придёт тело пакета. Таким образом, пакет идёт без остановок, минуя буфер. Low-swing signaling — это уменьшение разницы между напряжениями 0 и 1 в проводнике, за счёт чего удалось дополнительно сократить энергопотребление. В сумме эти усовершенствования поднимают пропускную способность и экономичность более чем в полтора раза.

Кроме улучшения таких характеристик, как энергопотребление и скорость, архитектура NoC даёт ещё одно важное преимущество. Она легко позволяет объединять не только однородные ядра, но и вообще любые блоки на одном чипе. Как и в компьютерных сетях, физический и транспортный уровни работают одинаково для любых типов данных и протоколов. Можно без особых проблем поставить на место одного или нескольких из универсальных вычислительных ядер любой другой IP-блок, например, графическое ядро, специализированный сигнальный процессор или контроллер какого-либо устройства. И, так же как и в сетях, можно реализовать поддержку Quality of Service на уровне чипа, что может быть полезно для систем реального времени и виртуализации.

NoC для объединения ядер процессоров пока ещё имеют экспериментальный статус, однако для объединения разнородных блоков в системах на кристалле NoC разрабатываются и применяются довольно давно. Решения таких компаний, как Sonics или Arteris используются в микросхемах Samsung, Qualcomm и даже Intel. Возможно, уже скоро сетевая архитектура начнёт вытеснять шины и из “святая святых” микроэлектроники — многоядерных центральных процессоров. И тогда число ядер снова начнёт стремительно расти. Так что закон Мура хоронить ещё рано.

Дополнительные источники по теме:

- Презентация Intel

- Список исследовательских групп, занимающихся NoC

- Компания Tilera — разработчик процессоров на архитектуре NoC

- Сравнение NoC и шинной архитектуры

- Обзорная лекция по NoC

Автор: ilya42