Если вы хотя бы раз слушали доклады FPGA Systems, вы знаете, что это настоящий интенсив с новыми знаниями по FPGA-разработке и не только. Заключительная конференция сообщества в этом году, организованная с YADRO, — не исключение. 30 ноября, в субботу, вас ждет восемь докладов от инженеров из МИЭТ, БЮРО 1440, ЭРЕМЕКС, YADRO. От новостей китайских ПЛИС (BMTI) — докладчик недавно посетил их производство — до разбора практических кейсов. Например, как запустить видеокарту AMD на ПЛИС с RISC-V.

Места на офлайн уже разобрали, но онлайн-трансляция доступна всем. Изучайте программу и подключайтесь к интересному именно вам докладу. И обязательно регистрируйтесь — так вы получите ссылку на трансляцию и ее запись после митапа.

Что в программе

Введение в проектирование RTL цифровых систем средствами Chisel/SCALA

Денис Муратов

Ведущий инженер по разработке СнК, YADRO

Многие из вас точно слышали про Chisel как альтернативу стандартным HDL для проектирования цифровых систем. Но бывает сложно разобраться, нужно ли использовать эту технологию, чем она может быть полезна или, наоборот, опасна для проектов. Я сделаю обзор Chisel: сравню его с System Verilog и расскажу, как несколько строк кода на Chisel позволяют генерировать сложные цифровые схемы. Объясню, почему эти схемы практически всегда работают и не требуют отладки.

Генерация преднамеренных ошибок в UVM-тесте

Андрей Ефимов

Ведущий инженер-верификатор, Бюро 1440

Во время верификации многих систем на базе FPGA/ASIC требуется смоделировать не только нормальную работу, но и работу при ошибочных воздействиях. Чаще всего нормальную работу проверяют с помощью автоматического тестирования, а для сценариев с ошибками нужны направленные тесты и ручная оценка результата. Процесс добавления ошибок хорошо описан в литературе, а вот оценку реакции системы обычно опускают, хотя это самое сложное.

Я расскажу о методе, который позволяет проводить автоматическое тестирование с добавлением случайных ошибок в воздействия и автоматически оценивать результаты. Это универсальный подход, который можно использовать в любом проекте.

Проектирование интегральной схемотехники в российских САПР

Никита Малышев

ЭРЕМЕКС, руководитель проекта системы цифрового моделирования и синтеза

Расскажу, почему вам стоит присмотреться к российской САПР проектирования ИМС в последних релизах.

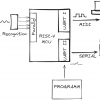

Как мы AMD GPU на ПЛИС с RISC-V Linux запускали

Сергей Мирошниченко

Руководитель отдела системного программирования, YADRO

За полчаса расскажу, как устроен PCIe и с чем пришлось разобраться перед запуском бенчмарка OpenGL. В докладе обсудим:

-

Проблемные места драйверов, которые мешают запуску где-то, кроме мира x86, и как их исправить.

-

Что делать, если не хватает 64 бит адреса.

-

Как подготовить свой стенд к DMA.

-

Как не захлебнуться прерываниями.

-

Какова практическая польза ветки master.

Open source Step-and-Compare: делаем индустриальный подход к верификации RISC-V доступным каждому

Сергей Чусов

Инженер по верификации НИЛ ЭСК НИУ МИЭТ

Расскажу про преимущества и недостатки современных индустриальных подходов к верификации ядер RISC-V. Подробно остановлюсь на Step-and-Compare и его реализации с помощью открытого ПО.

Увеличиваем производительность, искажая время: extended useful skew

Алексей Мухаматнабеев

Старший инженер отдела FPGA прототипирования, YADRO

Рассмотрим метод намеренного искажения тактового древа для увеличения рабочей частоты дизайна. Во время доклада поговорим о важности сбалансированности тактового древа, вспомним, что такое Useful Skew и что можно в него добавить, а еще посмотрим, как использовать этот метод, и разберем его ограничения.

Работаем на HDMI на ПЛИС

Алексей Гребенников

Независимый эксперт

Интерфейс HDMI есть на многих отладочных платах. Он позволяет получать значительно больше информации об их состоянии, чем, скажем, набор светодиодов. В докладе посмотрим на реализацию интерфейса HDMI на ПЛИС — Tx и Rx.

Что нового у BMTI?

Михаил Коробков

Ведущий митапа и «вождь» сообщества FPGA Systems

Недавно я вернулся их командировки на китайский завод BMTI. По свежим следам расскажу про обновление линейки «коммунистических» ПЛИС и не только.

Где и когда встречаемся

30 ноября, суббота. Начало конференции — в 11:00. Пришлем ссылку на трансляцию в VK, YouTube или Rutube после регистрации на сайте.

Что изучить перед конференцией

→ Синтез цифровых схем: что почитать при любом уровне подготовки

→ Итеративная сборка FPGA-проектов

→ Quake 2 на нашем RISC-V, или как мы поднимали старый Radeon на FPGA

→ Запускаем Embedded Linux на Hard- и Soft-CPU Xilinx Zynq: проект программируемой логики и сборка ОС

Автор: yadro_team