В течении последнего года я запустил серийные проекты на микроконтроллерах CH32V207 и CH32V203. И в том или ином виде попробовал работать почти со всеми RISK-V ядрами от WCH. Анализ опыта работы, это отдельная история, сейчас хотел бы рассказать про структуру памяти старшей линейки WCH. В первую очередь, потому что, я, даже в сегменте англоязычных форумов, не нашел полной информации на эту тему. А небольшой объем памяти анонсируемый в даташитах, возможно многих отпугивает.

Память, которая то ли есть, а то ли ее нет?

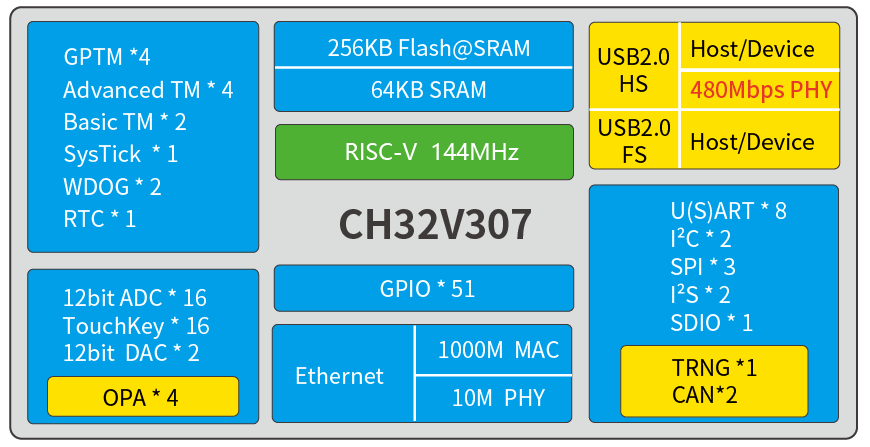

В датишитах значится достаточно скромный объем FLASH. От 64кБ до 256кБ в зависимости от модели.

Несколько смущает только надпись Flash@SRAM.Но дальше по тексту этого уточнения нет. И вроде все очевидно. Но тут я решил поиграться в Ble и запустил примеры для СH32V208, где анонсирован флэш в 128кБ. Собственно SDK к этому ядру стандартный от V2XX, за исключением Ble, который скопирован с Ble ядер СH5XX и аналогичных. Сборка любого примера Ble https://github.com/openwch/ch32v20x/tree/main/EVT/EXAM/BL, приводит к тому, что код занимает больше 128кБ. Ошибок при этом нет, и если посмотреть линк файл, видно что там объявлены 480кБ флэш памяти. Не понятно. 480кб флэша, это же про 20Mhz Ble чип СH582, но при чем тут V208? Тем более что в примерах для обычной периферии, линк файл собирает код в сегмент размера 128кБ.

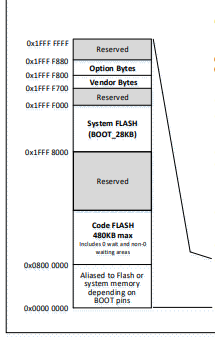

Дальше, если внимательно присмотреться к документации по V3XX, то можно найти маленькую сноску про разделение FLASH на zero-wait и non-zero-wait.

Действительно, 480кБ флэш. В аналогичных документах по семейству V2 завялены более скромные 256К (при 64кБ по даташиту). Это все легко проверить, подключившись к чипу программатором. Совсем непонятно что происходит...

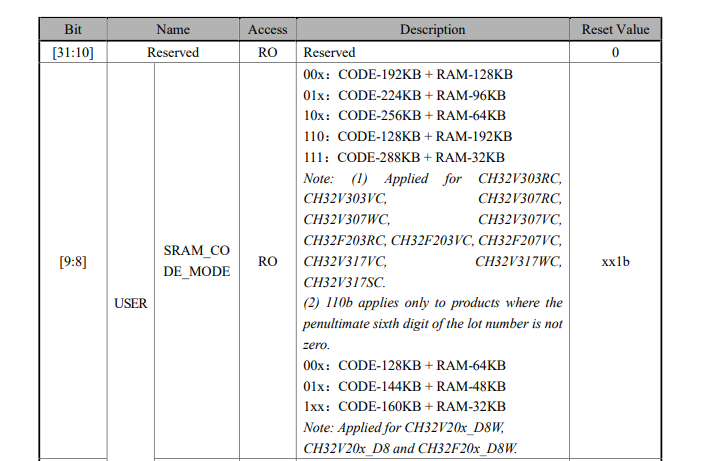

Ответ про структуру памяти приходит при работе со старшими ядрами, в том числе V307.Для этих контроллеров возможно настройка конфигурации памяти.

Таким образом, в CH32V307 реально 320кБ SRAM, часть из которой используется как кэш FLASH памяти. На каком уровне происходит копирование флэш в статику я информации так и не нашел.

Итого имеем следующие. Все микроконтроллеры V2XX и V3XX оснащены флэшем, размером 224кБ или 480кБ. Часть из него при старте автоматический кэшируется в статическую память и исполнение кода идет из статики. Реальный размер статической памяти во всех контроллерах, SRAM (по документации) + FLASH ( по документации). В более младших моделях статики меньше, и кэшируется меньший объем флэша. В более старших он доходит до 320Кб, и есть возможность изменить распределение SRAM. Либо больше памяти данных, но не более 128К, либо больше отдать под кэшируемый флэш. А что собственно, с оставшимся флэшем, который не попадет в кэш? А ничего, можно использовать.

Но есть нюанс.

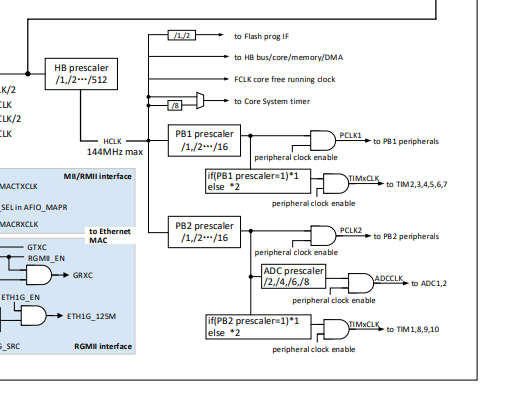

Физический флэш тактируется от системный шины и делитель может быть 1 или 2, при максимальной частота тактирования флэш 60МhZ. Поэтому для использования этой области, частота системной шины не должна превышать 120Mhz. Максимальная частота для WCH в 144Mhz сразу отпадёт. Более низкие частоты тактирования системной шины, дадут скорость доступа к физическому флэшу ниже максимальной. При этом не стоит забывать про периферию, частоты тактирования SPI и AЦП к примеру ограничены. А делители периферийных шин переехали из STMF103, c родной частотой в 72Mhz. Фактический, использовать вот вообще все на максимальных частотах одновременно не получиться, продеться искать какой-то компромисс. Мне лично не нужны максимальные частоты АЦП и SPI, а вот дополнительный флэш может пригодиться.

Как этот флэш использовать, уже вопрос. В родном SDK для Ble, объявлен отельной сектор, распложённый в кэшируем флэше, куда линкуется TMOS, операционная система стека Ble (хотя это не совсем ОС). Все остальное собирается линейно, без контроля куда что попадает. В листингах видно, что функция начинается в кешируем флэше, а заканчивается в медленном... Я в своем коде наоборот объявил сектор для медленного флэша, куда скидываю инициализацию.

В глубины, насколько медленный флэш снижает производительность я пока не копал. Но по итогу, думаю что наличие пусть более медленного, но все таки приличного объема доп. флэша, существенно может расширить сферы применения микроконтроллеров WCH.

Автор: Smoke666