Если вы ещё не в курсе, то недавно было объявлено о выходе Raspberry Pi 5.

Я специально снял ролик, где разобрал всю аппаратную часть – что изменилось, что появилось и чего не стало. В этой статье я представлю вам спецификацию новой модели, расскажу о некоторых особенностях и о том, что выяснил в ходе тестирования её работы с десятком различных устройств PCIe.

▍ Спецификация / сравнение с Pi 4

| Raspberry Pi 4 | Raspberry Pi 5 | |

| CPU | 4x Arm A72 @ 1.8 GHz (28nm) | 4x Arm A76 @ 2.4 GHz (16nm) |

| GPU | VideoCore VI @ 500 MHz | VideoCore VII @ 800 MHz |

| RAM | 1/2/4/8 GB LPDDR4 @ 2133 MHz | 4/8 GB LPDDR4x @ 4167 MHz |

| USB | USB 2.0 (общий), USB 3.0 (общий) | 2x USB 2.0, 2x USB 3.0 |

| PCIe | (внутреннее использование) | PCIe Gen 2.0 x1 |

| Южный мост | N/A | RP1, распределяющий 4 канала PCIe Gen 2.0 |

| Ethernet | 1 Gbps | 1 Gbps (с поддержкой PTP) |

| Wifi/BT | 802.11ac/BLE 5.0 | 802.11ac/BLE 5.0 |

| GPIO | 40-контактная гребёнка, подключение через BCM2711 | 40-контактная гребёнка, подключение через южный мост RP1 |

| Fan | 5v через GPIO, без ШИМ | 4-контактная гребёнка, с ШИМ |

| UART | через GPIO, требуется настройка | через гребёнку UART напрямую к SoC |

| Цена | $35 (1GB) / $45 (2GB) / $55 (4GB) / $75 (8GB) | $60 (4GB) /$80 (8GB) |

▍ Обзор Pi 5

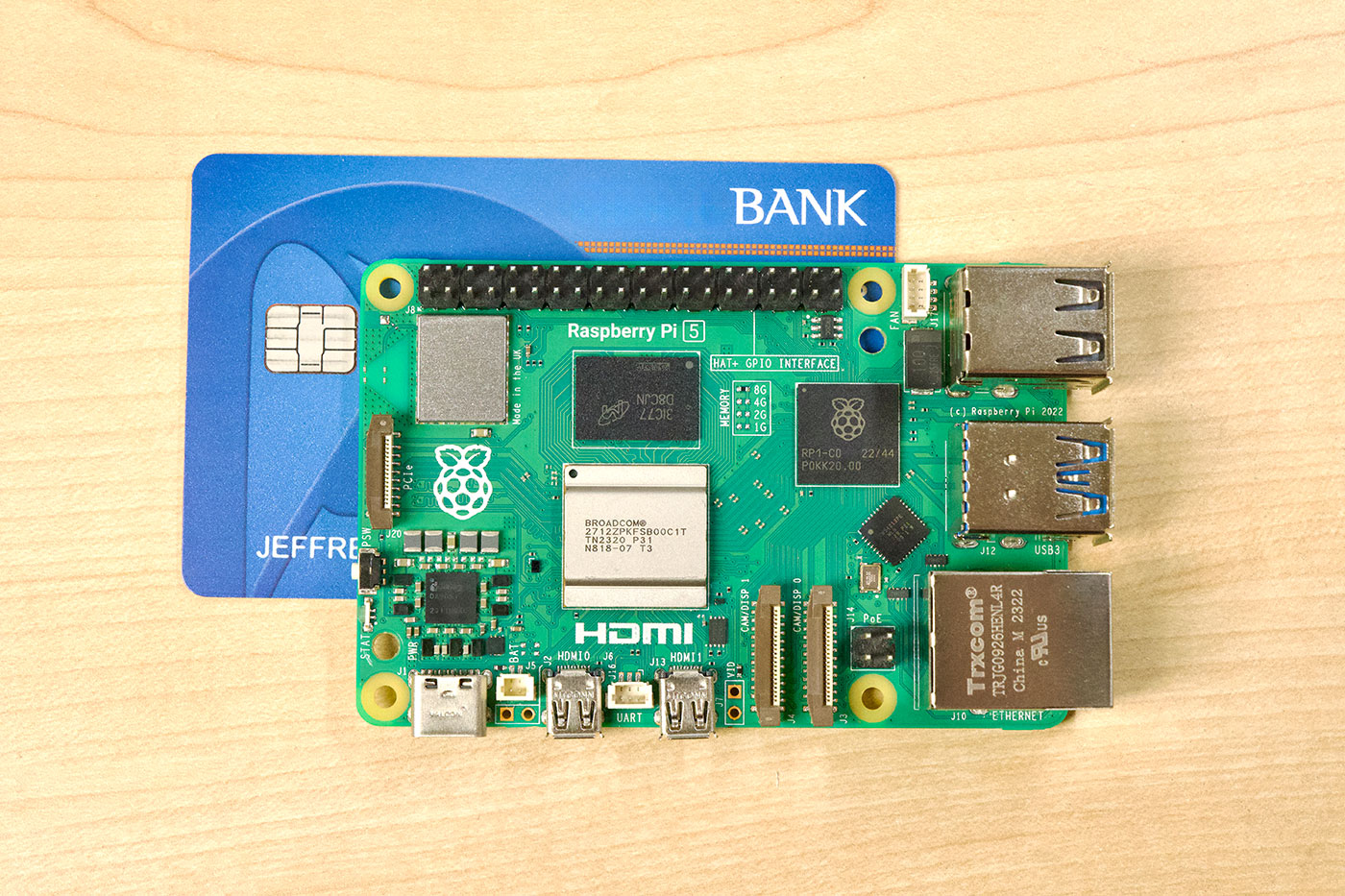

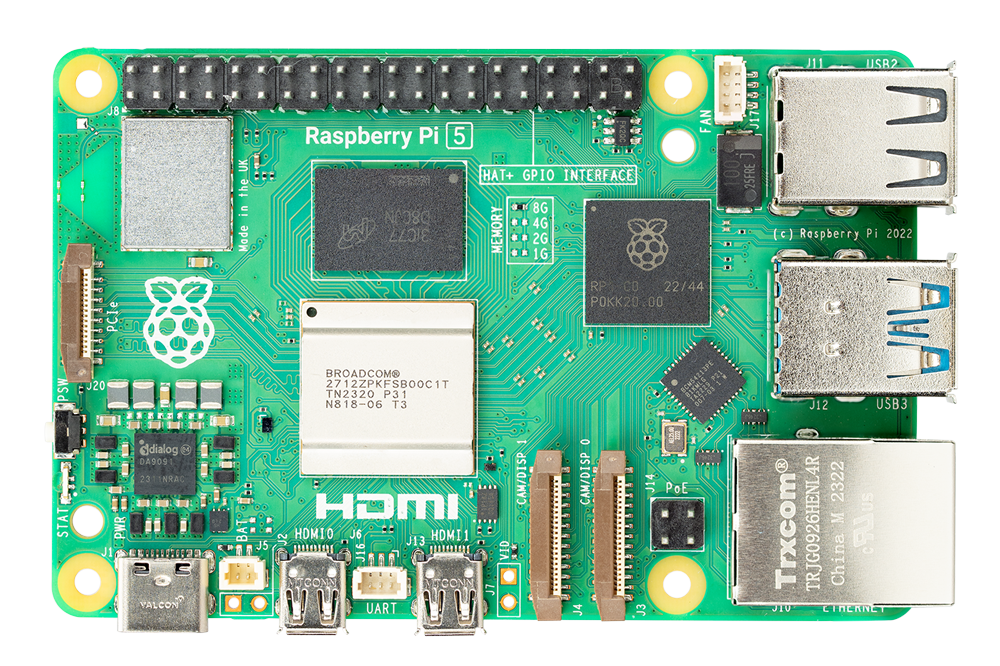

Raspberry Pi 5 model B, как и прошлые модели, по-прежнему имеет размер с кредитную карточку, но на сей раз вмещает в это крохотное пространство дополнительную функциональность, включая RTC, кнопку питания, отдельную гребёнку UART, 4-контактный разъём под кулер, FPC-разъём PCIe, два FPC-разъёма CSI/DSI двойного назначения и четыре независимых шины USB (по одной для каждого из 2 портов USB 3.0 и 2 портов USB 2.0).

Что изменилось:

- гнездо Ethernet развернули в том же направлении, что и в Pi 3 B+ и более ранних моделях;

- два светодиода ACT/STATUS стали одним STAT, изменяющим цвет;

- контроллер VL805 USB 3.0 был заменён южным мостом RP1, к которому от новой SoC BCM2712 идут 4 канала PCIe, распределяемые им по всем интерфейсам;

- гнездо A/V убрали, установив на его место гребёнку для вывода аналогового видео;

- порты CSI и DSI тоже убрали, заменив двумя портами CAM/DISP двойного назначения, обеспечивающими бо́льшую пропускную способность и гибкость использования (теперь можно напрямую подключать к Pi стереоскопическую камеру);

- микросхему PMIC улучшили, и теперь она поддерживает входную мощность USB-C 25 Вт при 5 В/5 А (разработчики предлагают для этого новый блок питания, хотя можно использовать и прежнюю модель на 3 A).

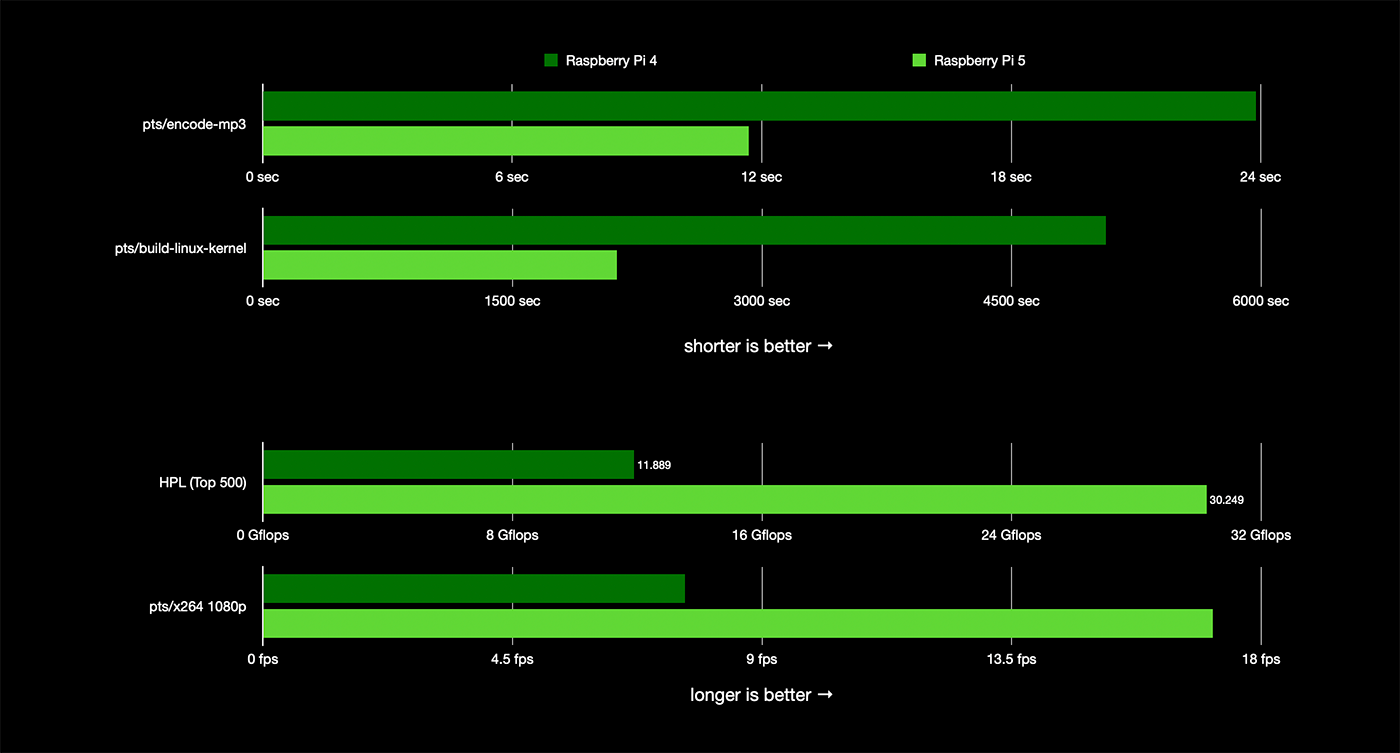

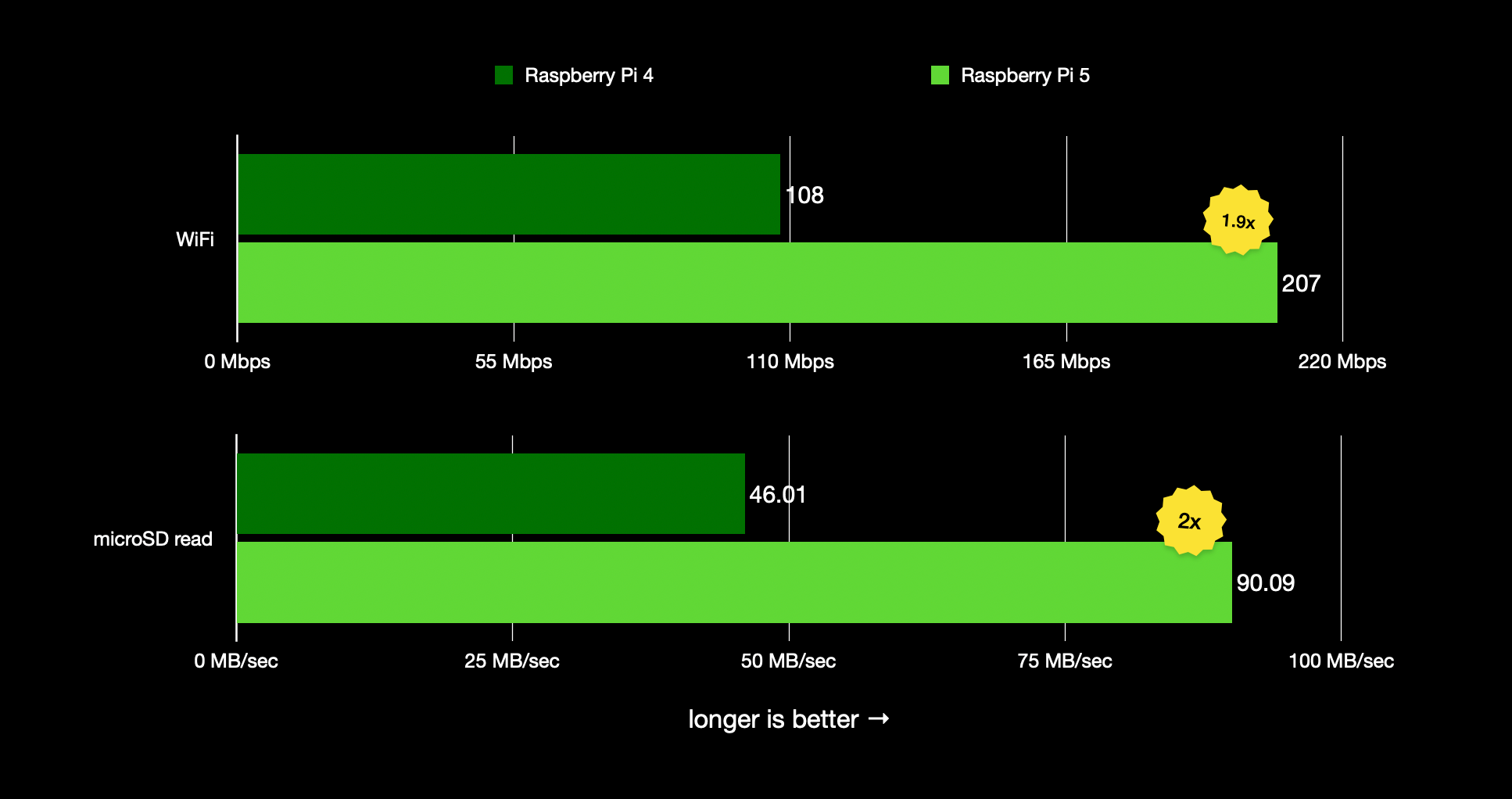

Pi 5 в 2-3 раза быстрее Pi 4 по всем значимым показателям:

- SoC работает в 1,8 – 2,4 раза быстрее во всех опробованных мной бенчмарках процессора и системы;

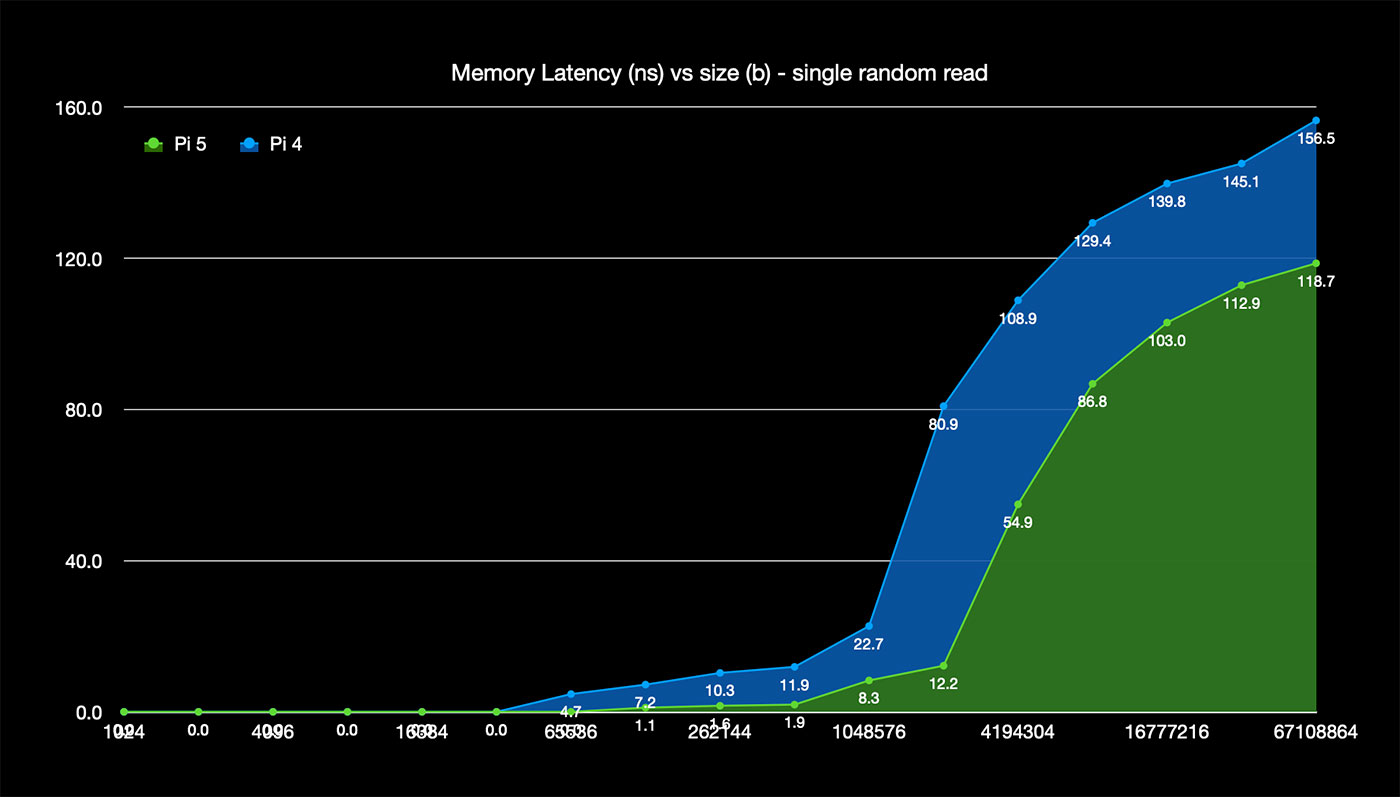

- скорость LPDDR4X вдвое выше (при пониженном напряжении) по сравнению с LPDDR4 в Pi 4, что примерно в 2-4 раза ускоряет доступ к памяти и значительно сокращает задержку;

- общая пропускная способность USB удвоилась за счёт четырёх независимых шин;

- производительность HDMI также удвоилась, и теперь можно без тормозов воспроизводить 4K @ 60 Гц, параллельно выполняя другие задачи (у Pi 4 возникали проблемы даже при 30 Гц);

- слот microSD соответствует стандарту UHS-I (SDR104) и обеспечивает вдвое большее быстродействие в сравнении с Pi 4, достигая 104 МБ/с;

- скорость работы WiFi тоже удвоилась – я смог получить 200 Мбит/с по 5 ГГц 802.11c против 104 Мбит/с на Pi 4.

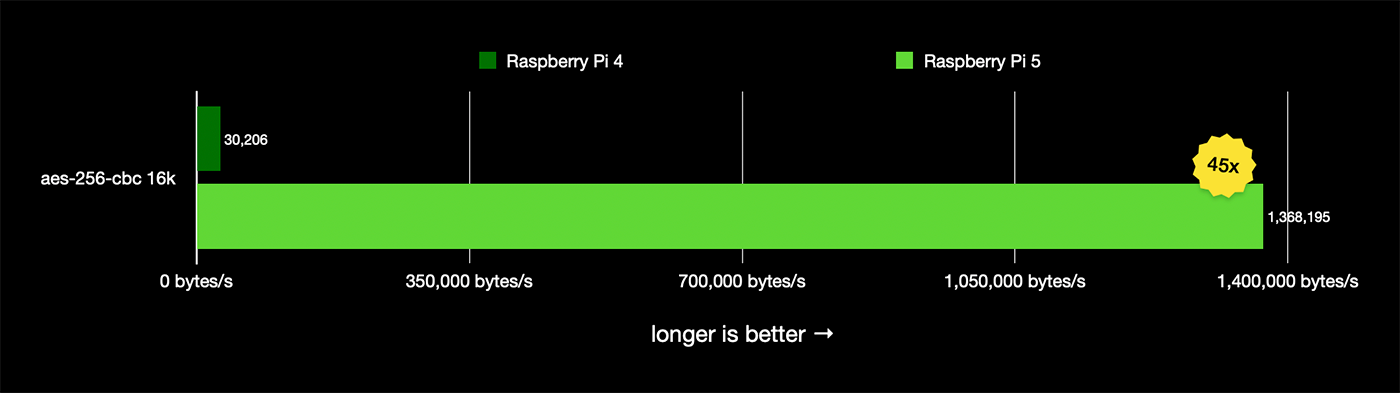

Криптографические функции здесь работают в 45 раз быстрее, благодаря расширениям Arm, которые, наконец-таки, были добавлены в систему Pi 5:

▍ Pi 5 и Raspberry Pi OS 12 «Bookworm»

Pi 5 ориентирован на оптимальную работу с Pi OS 12 «Bookworm» (основанную на одноимённом релизе Debian), и во время альфа-тестирования мы сталкивались с рядом проблем – некоторые из которых могут попасть в серийную версию, поскольку существуют давно и также затрагивают другие системы, основанные на архитектуре Arm.

Одной из них является решение опробовать размер страницы 16 Кб, что слегка повышает быстродействие за счёт частичной утраты совместимости со старыми бинарниками под armv7/32 бита. Не знаю, будет ли в итоге Pi OS 12 использовать страницы 16 Кб, но при необходимости есть способы добавить совместимость с более старым ПО.

Ещё одна проблема – это использование устаревших библиотек и утилит вроде tvservice и wpa_supplicant вместо более современных альтернатив, таких как kmsprint и NetworkManager.

▍ Изучаем возможности PCIe

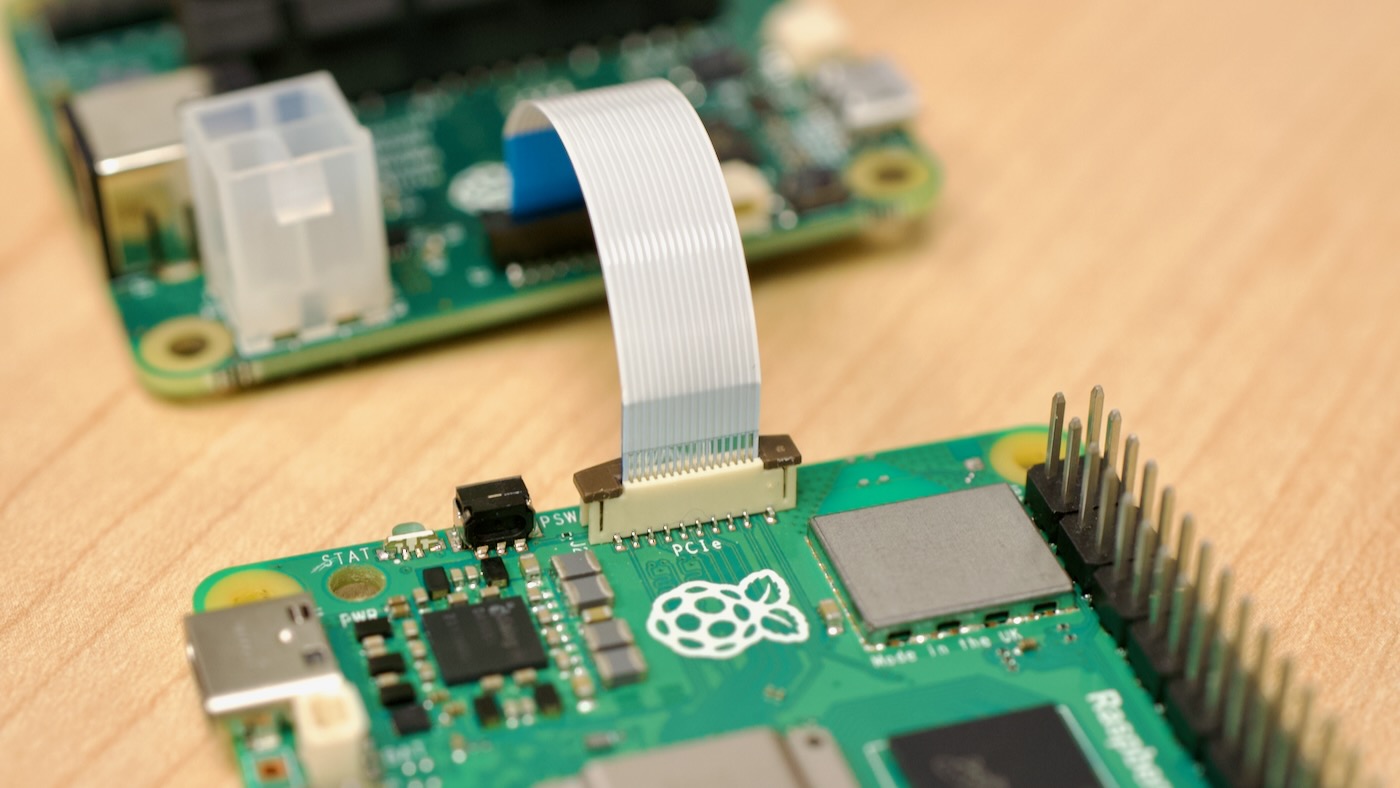

Вот мы и добрались до самого интересного для меня новшества Pi 5 – линии PCI Express, которая теперь стала доступна для пользователей.

Внимательное изучение спецификации RP1 показывает, что в ней используется 4 канала PCIe Gen 2, исходящих от SoC BCM2712. Это значит, что фактически на плате присутствует пять каналов PCIe. Однако для пользователя доступен только один – через FPC-разъём, показанный на фото выше.

По умолчанию внешняя гребёнка PCIe не активна. Для её включения нужно добавить в файл /boot/config.txt одну из следующих опций, после чего перезагрузить устройство:

# Активация внешнего разъёма PCIe.

dtparam=pciex1

# Эта строка является псевдонимом для команды выше (для активации порта можно использовать и ту, и другую).

dtparam=nvmeПри этом подключение сертифицировано под Gen 2.0 (5 GT/sec), но вы можете расширить его возможности до Gen 3.0 (10 GT/sec), добавив следующую строку:

dtparam=pciex1_gen=3Я делал так во многих тестах без каких-либо проблем. Думаю, если не брать в расчёт какие-то изощрённые тесты, то устройства, успешно прошедшие стандартное тестирование, будут стабильно работать и на скоростях Gen 3.0.

Сейчас для PCIe ещё нет модулей HAT (Hardware Attached on Top, таких как M.2, Mini PCIe и так далее), но я смог одолжить для тестирования отладочный адаптер от Raspberry Pi. Надеюсь, что вскоре появятся новые HAT для различных высокоскоростных периферийных устройств (как это произошло с платами Computer Module 4, когда в них появилась возможность использовать PCIe).

Если вы захотите собрать собственный HAT для PCIe, то учтите один подвох: FPC-разъём обеспечивает на своей линии 5 В не более 5 Вт, так что напрямую через него запитать много устройств не получится. Лично я для подачи питания на отладочную плату использовал круглый разъём 12 В.

Далее я расскажу про каждое протестированное мной устройство отдельно. Отмечу, что пока у меня не было достаточно времени для проведения реальной отладки, как в случае с Compute Module 4. В конечном же итоге я планирую разместить все полученные данные на сайт в раздел Raspberry Pi PCIe Devices.

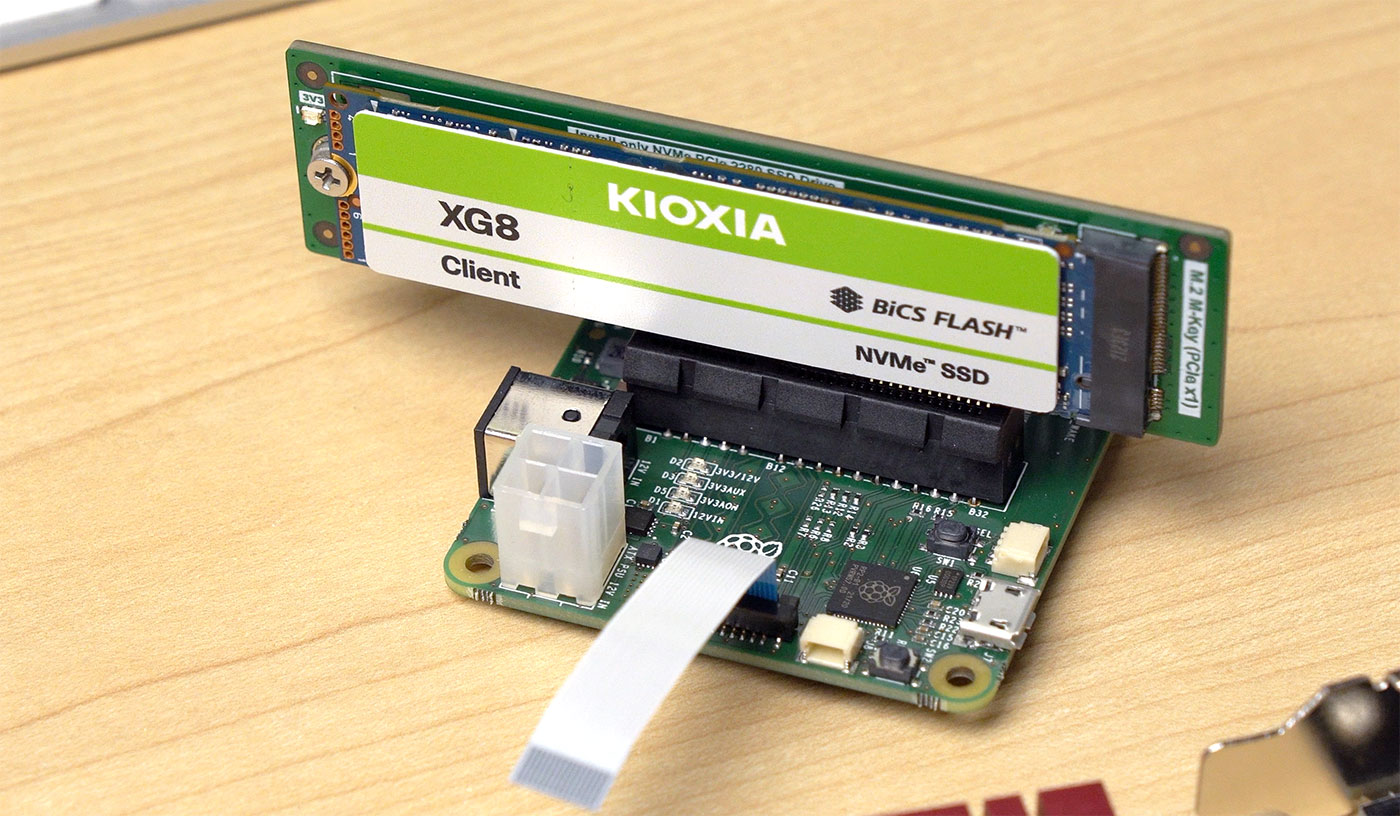

▍ NVMe SSD

Загрузка с NVMe SSD вместо встроенной карты microSD, пожалуй, будет основным случаем использования PCIe в Pi 5, по крайней мере, поначалу.

Я испробовал несколько разных SSD с поддержкой Gen 3 и Gen 4, остановившись на показанном выше KIOXIA XG8, так как он работает наиболее эффективно.

При базовой скорости PCIe Gen 2.0 я смог получить 450 МБ/с, и почти достиг 900 МБ/с, задействовав неподдерживаемый Gen 3.0.

Бо́льшую часть тестов Pi 5 я проводил, загружаясь с этого SSD, и позже опубликую отдельную статью, посвящённую загрузке этого девайса через NVMe. Она поддерживается из коробки, но требует изменения порядка загрузки в EEPROM.

Здесь я столкнулся с одной проблемой, которую на момент написания статьи так и не смог решить. Дело в том, что во время использования NVMe интерфейс WiFi brcfmac не инициализируется должным образом (вне зависимости от того, откуда происходит загрузка: с NVMe, microSD или USB). В случае других протестированных устройств PCIe встроенный WiFi инициализировался нормально. Я считаю, что проблема может быть связана с тем, как запитан используемый прототип адаптера PCIe.

Надеюсь поскорее увидеть первые HAT под NVMe – и если этого не произойдёт, готов заплатить первому, кто такой преобразователь соберёт. Будет очень удобно, если получится установить в Pi 5 слот M.2. Запитывание SSD может создать трудности, поскольку многие устройства NVMe потребляют более 5 Вт.

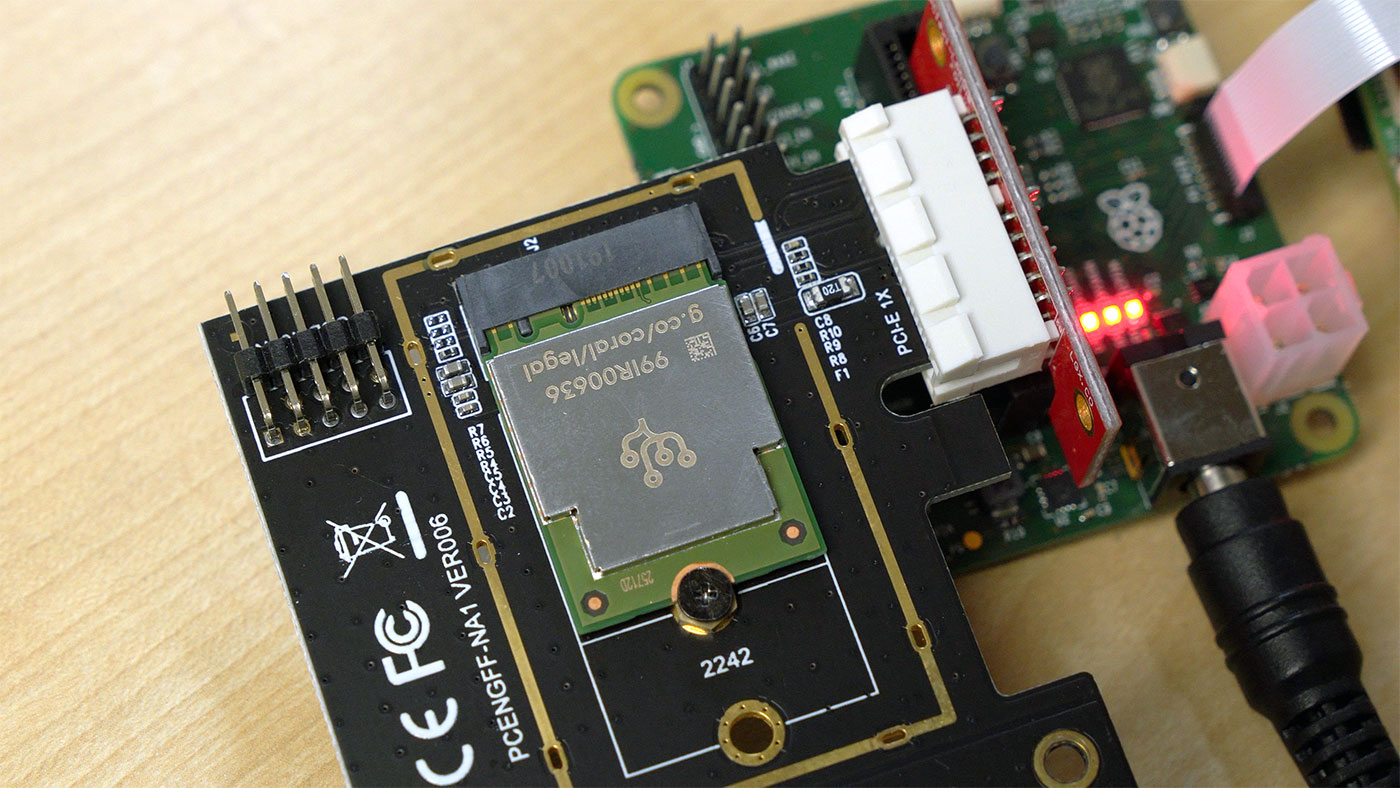

▍ Coral TPU / Нейроускорители

Coral TPU зачастую используются совместно с Frigate для обнаружения объектов с помощью ИИ. USB-устройства Coral работали со всеми моделями Pi долгие годы, но у версий PCIe наблюдались проблемы с функционированием на слегка дефектной шине PCIe в Compute Module 4.

Следуя официальной инструкции Coral, я смог установить в Pi 5 модуль ядра apex, но в логах регулярно выводилось сообщение об ошибке:

[ 72.418344] apex 0000:01:00.0: Apex performance not throttled due to temperature

[ 77.534508] apex 0000:01:00.0: Apex performance not throttled due to temperature

[ 77.534543] pcieport 0000:00:00.0: AER: Corrected error received: 0000:00:00.0

[ 77.534554] pcieport 0000:00:00.0: PCIe Bus Error: severity=Corrected, type=Data Link Layer, (Transmitter ID)

[ 77.534557] pcieport 0000:00:00.0: device [14e4:2712] error status/mask=00001000/00002000

[ 77.534560] pcieport 0000:00:00.0: [12] Timeout

[ 82.654615] apex 0000:01:00.0: Apex performance not throttled due to temperatureК слову: ненавижу, когда код продакшена засоряет системный журнал сообщениями об ошибках. Мне не нужно каждые пять секунд напоминать о том, что TPU не перегревается.

Выяснив, что pycoral несовместим с Python 3.11 (версия в Bookworm), я решил протестировать Coral TPU в Docker.

Проведя кое-какую отладку и заново всё переподключив – поскольку целостность сигнала в случае Coral, похоже, была более важна – я почти заставил его заработать:

[ 372.628183] pcieport 0000:00:00.0: AER: Corrected error received: 0000:00:00.0

[ 372.628199] pcieport 0000:00:00.0: PCIe Bus Error: severity=Corrected, type=Data Link Layer, (Transmitter ID)

[ 372.628204] pcieport 0000:00:00.0: device [14e4:2712] error status/mask=00001000/00002000

[ 372.628209] pcieport 0000:00:00.0: [12] Timeout

[ 373.268131] apex 0000:01:00.0: RAM did not enable within timeout (12000 ms)

[ 373.268141] apex 0000:01:00.0: Error in device open cb: -110

[ 373.268160] apex 0000:01:00.0: Apex performance not throttled due to temperatureОчевидно, что одна из лабораторных плат Pi 5 с Coral работает, но, похоже, моя экспериментальная плата, как и несколько тестовых, имеют проблемы с подключением. В случае большинства устройств PCIe периодическая потеря пакетов обрабатывается хорошо. А Coral, как мы видим, при каждом возникновении проблемы стремится повторить обучение и на моём устройстве никогда не доводит дело от начала и до конца.

Я попробовал снизить скорость до PCIe Gen 1 (2.5 GT/s), установив dtparam=pciex1_gen=1 в /boot/config.txt, но ошибка не исчезла. Скорее всего, проблему удастся решить за счёт более качественного FPC-подключения или платы адаптера.

Должен ещё раз напомнить, что использую первый прототип платы адаптера PCIe – проблемы с передачей сигнала, с которыми я столкнулся, в продакшен-версии наверняка будут устранены.

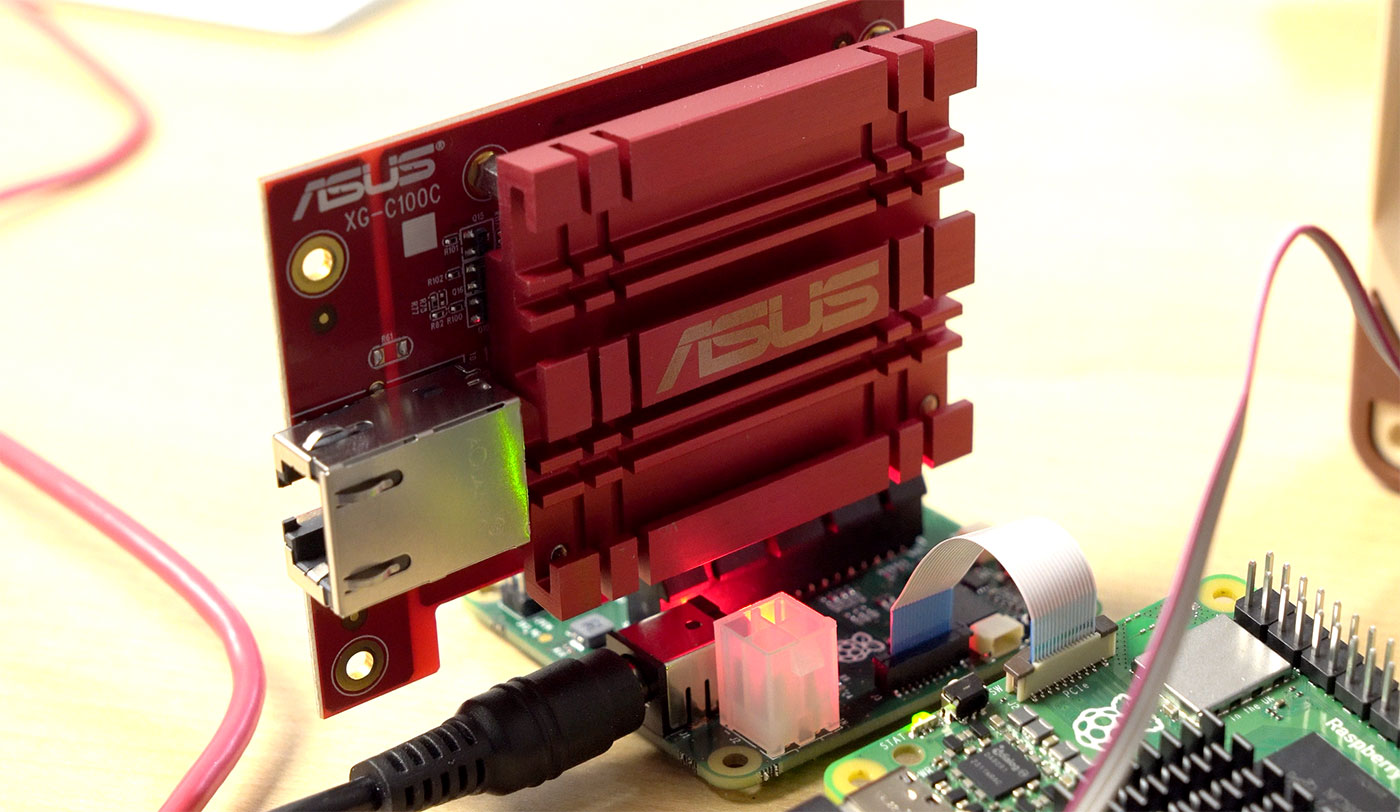

▍ Сетевые карты

Похоже, что проблемы с передачей сигнала никак не повлияли на эту карту Asus 10G. Чтобы она заработала, я пересобрал ядро Linux, добавив необходимые модули Aquantia (читайте мой гайд).

После установки карта сразу определилась, и при скорости PCIe Gen 3 я смог получить 5,5 – 6 Гбит/с. Предполагаю, что существует карта 10G, которая сможет приблизиться к передаче до 10 Гбит/с по этому каналу, но я такую не нашёл.

Другие карты (вроде проверенной Intel I340-T4, которую я использовал в CM4 для установки четырёх гигабитных подключений) тоже заработали исправно, так что с сетью я ещё особо не возился.

Думаю, что Pi отлично подружится с двухпортовой картой 2,5 Gigabit от Syba. У меня такая есть, но пока я её не тестировал. Надеюсь, кто-нибудь соберёт Router HAT с двумя интерфейсами 2,5 G и убедит разработчиков OPNsense/PFsense выпустить сборку под arm64.

Вы также можете добавить дополнительные интерфейсы через USB 3.0 – хотя в ходе короткого тестирования одного адаптера 2,5 G мне почему-то удалось добиться передачи всего 1.5 G.

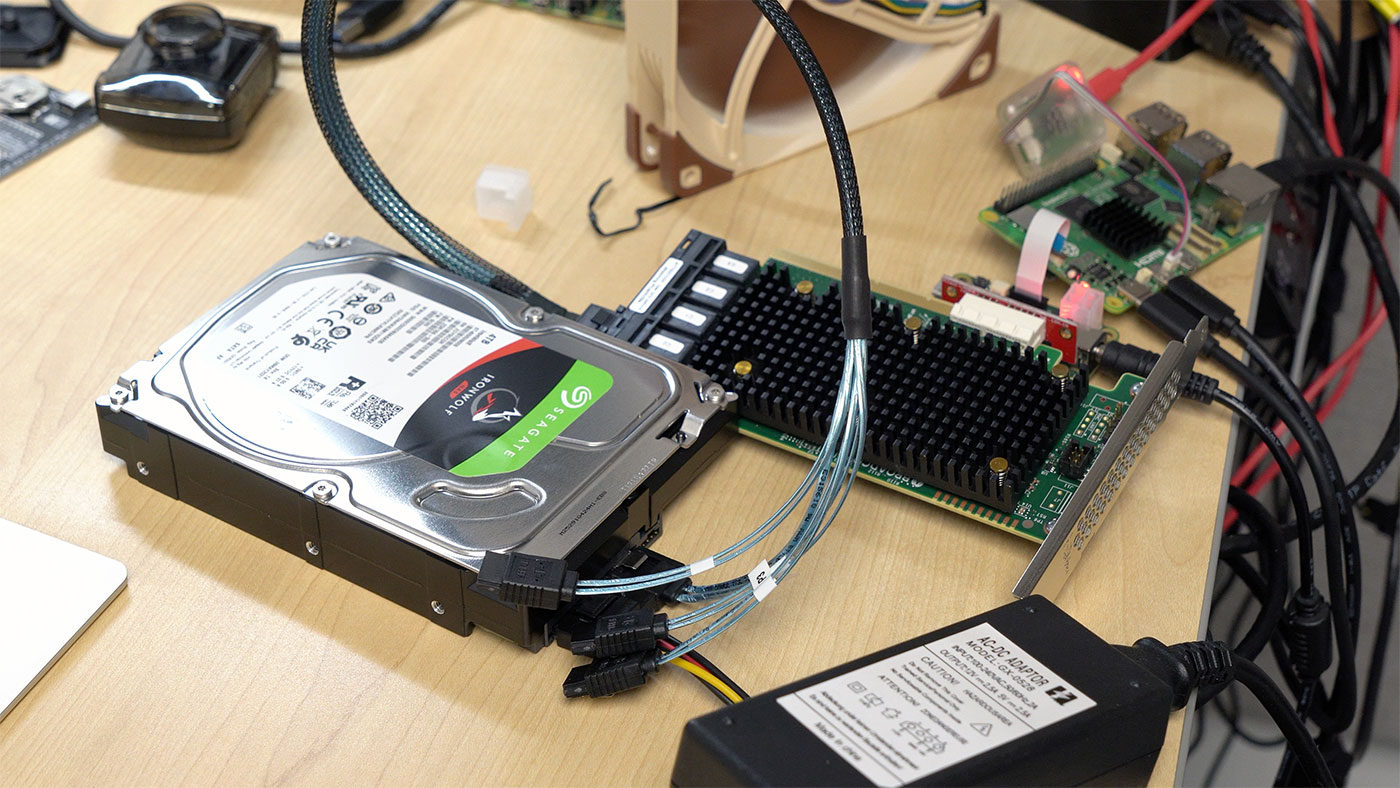

▍ Карты памяти HBA/RAID

Помимо прочего, я подключил через карту с RAID и HBA один SATA-диск, чтобы понять, будет ли драйвер mpt3sas от Broadcom (бывшая LSI) работать из коробки (в CM4 потребовался патч для исправления вот этого бага). Я протестировал одну из карт 9405W-16i, которые использовал в проекте Petabyte Pi, и ядро её распознало…а вот storcli почему-то нет.

У меня пока не было времени полноценно заняться отладкой, а поскольку то же самое произошло с 9460-16i, то вскоре я к этому вернусь. Хочу собрать ещё один собственный NAS на базе Pi 5, чтобы понять, смогу ли решительно преодолеть гигабитный барьер скорости записи по сети (которую Samba может выдавать на BCM2711!).

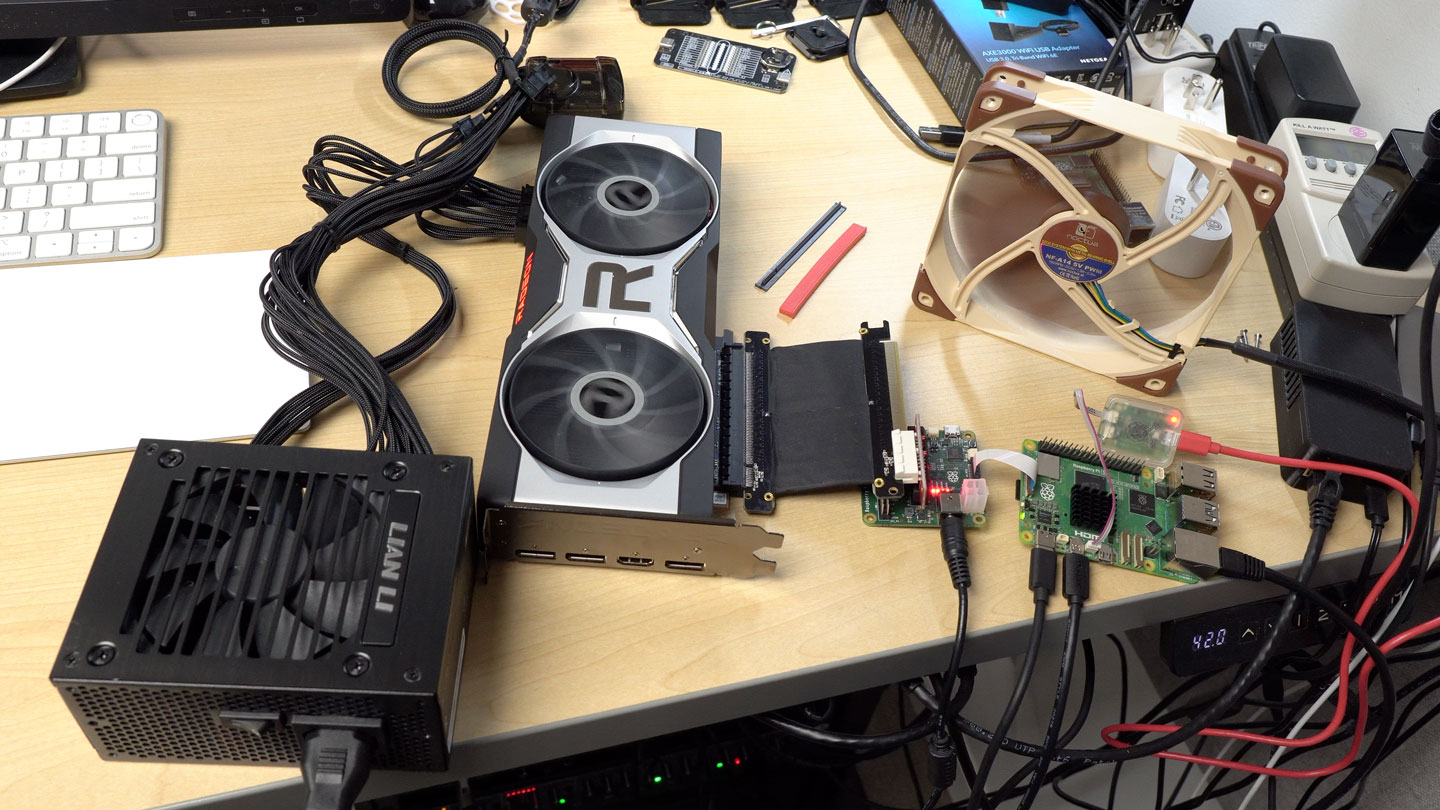

▍ Видеокарты

Те, кто следит за моими разборами Pi, знают все неявные проблемы, с которыми я сталкивался, налаживая работу видеокарт на Pi CM4. После огромного объёма тестирования различных карт – чаще не без чужой помощи – для нескольких старых карт нам-таки удалось получить частичный доступ к самым простым задачам рендеринга.

В мою рабочую станцию ADLINK Ampere Altra Max можно установить современную карту Nvidia. Как минимум на Ubuntu официальные драйверы arm64 загружаются без проблем, делая возможным гейминг и вычисления с GPU-ускорением.

Может ли то же самое Pi 5? Надеюсь, что да. На CM4 многие проблемы с драйверами приводили к полной блокировке Pi.

Но теперь всё иначе, поскольку драйверы nouveau, nvidia, amdgpu и radeon – все успешно идентифицировали подключаемые мной видеокарты. Драйверы Nvidia встают чётко, а lspci показывает, что модуль загружается исправно.

Но я всё же столкнулся с сообщением об ошибке RmInitAdapter failed!, которое уже досаждало мне ранее. Как бы здесь пригодился опенсорсный драйвер под Linux!

Подождите-ка! У AMD такой есть! Интересно, как он справится?

В ходе тестирования RX 6700 XT с опенсорсным драйвером AMDGPU, включенным в Linux, возникло несколько ошибок:

[drm:psp_hw_start [amdgpu]] *ERROR* PSP load kdb failed!

[drm:psp_v11_0_ring_destroy [amdgpu]] *ERROR* Fail to stop psp ring

[drm:psp_hw_init [amdgpu]] *ERROR* PSP firmware loading failed

[drm: amdgpu_device_fw_loading [amdgpu]] *ERROR* hw_init of IP block <psp> failed -22

amdgpu 0000:03:00.0: amdgpu: amdgpu_device_ip_init failed

amdgpu 0000:03:00.0: amdgpu: amdgpu: finishing device.Но я думаю, что мы очень близки. Некоторые из этих проблем также, по всей видимости, связаны с таймингом, что может относиться к недостаточной целостности сигнала моего прототипа переходника PCIe. Я определённо намерен приобрести более качественный шлейф FFC (Flexible Flat Cable) с экранированием.

Как я слышал, HAT под PCIe и более качественные кабели уже разрабатываются, но мой интерес к появлению PCie в Pi сейчас не стоит во главе угла, так как в этой модели и без того появилось с десяток других подсистем и новейшая микросхема южного моста RP1.

▍ Заключение

В этой статье мы познакомились с темой лишь поверхностно – я провёл ещё много часов за тестированием и отладкой различных компонентов Pi 5, описав всю работу в видео, посвящённом Raspberry Pi 5. Рекомендую его посмотреть.

Автор: Дмитрий Брайт