Компания GlobalFoundries отказалась от гонки за техпроцессами и замерла на отметке 12 нм, но это не означает, что она не будет внедрять передовые технологии объёмной упаковки чипов. За счёт 3D-компоновок даже старый техпроцесс можно использовать таким образом, что результирующий чип даст фору новейшим техпроцессам. Например, гибридные 90-нм чипы на углеродных нанотрубках обещают на равных соперничать с 7-нм FinFET-чипами, что достигается за счёт комплексности 3D-сборок. Тем самым действие закона Мура может быть продлено даже без перехода на более тонкие техпроцессы. Достаточно наращивать «этажность» чипов и повышать число транзисторов на каждый квадратный миллиметр в основании кристалла.

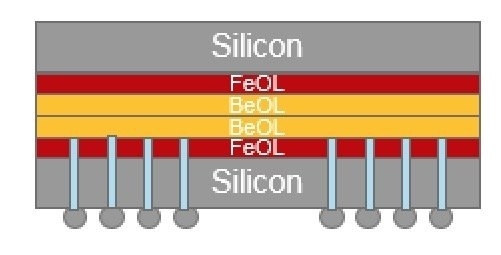

Пример упаковки Wafer on Wafer (Cadence)

Возвращаясь к GlobalFoundries, сообщим, что она и ARM вместе закончили проектировать тестовый чип в объёмной (3D) упаковке. Чип предназначен для демонстрации возможностей производства составных и гибридных решений для мобильной и вычислительной техники, включая ИИ и машинное обучение. Судя по тому, что GlobalFoundries доложила о выполнении этапа taped-out, решение существует только в виде цифрового проекта, а не в кремнии. Впрочем, для тестирования проекта с получением характеристик этого уже достаточно.

Для сборки 3D-упаковки использована фирменная методология GlobalFoundries Design-for-Test (DFT). Два (судя по всему) кристалла соединены «лицом к лицу» по технологии wafer-to-wafer. К слову, компания TSMC также собирается использовать данный вид соединения кристаллов (пластин), когда связь между кристаллами сводится до коротких соединений в их толще с выходом контактов для связок «этажей» на поверхность. Это делается в противовес довольно длинным и сравнительно толстым сквозным TSVs соединениям, не говоря уже о традиционной обвязке с соединением через несколько металлических слоёв BeOL.

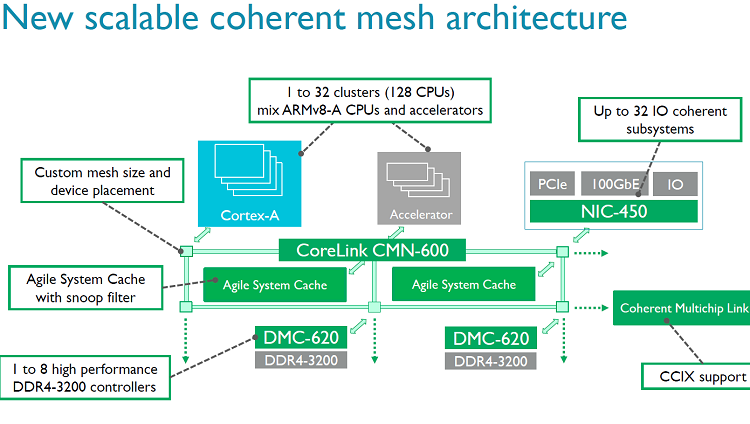

Ячеистая сетевая архитектура ARM

Ближе всего соединения wafer-to-wafer подошли к сборке кристаллов 3D NAND из двух или трёх кристаллов в условно монолитные чипы с большим числом слоёв (в 64-слойные из двух 32-слойных, в 96-слойные из двух 48-слойных и так далее). Для технологии GlobalFoundries в рамках 12-нм техпроцесса 12nm LP FinFet заявлено до 1 млн соединений на каждый миллиметр поверхности. Компания ARM, со своей стороны, предоставила в распоряжение партнёра технологию ячеистой сети, которая отвечает за согласованную работу блоков на всех этажах. Обе они предлагают воспользоваться 3D-технологией упаковки DFT wafer-to-wafer всем желающим, которым будут нужны высокопроизводительные решения с минимальным уровнем задержек в архитектуре.