Микроархитектура Cannon Lake способна обеспечить исполнение большего числа инструкций за такт (IPC) по сравнению с микроархитектурой Skylake. Прирост составил примерно 2–6 %. Компания Intel об этом не упоминает, поэтому эти изменения были обнаружены экспериментально. В данном случае были проведены измерения задержек и скорости исполнения каждой из инструкций процессора.

Для измерения латентности процессоров Skylake-SP и Cannon Lake использовалась встроенная в AIDA64 специализированная утилита для анализа микроархитектуры. После был проведён анализ и обнаружены некоторые изменения, присущие микроархитектуре Cannon Lake. Изменения коснулись сразу нескольких областей.

Целочисленное деление (DIV/IDIV) традиционно реализовано с помощью микрокода. В зависимости от значений входных регистров деление может занять до 90 тактов для микроархитектуры Skylake. В свою очередь Cannon Lake получил улучшенный микрокод, благодаря чему процесс деления сократился до 10–18 тактов.

В Cannon Lake увеличилась скорость исполнения некоторых инструкций копирования векторных регистров. Это стало возможным за счёт изменения механизма исполнения данных команд. В Skylake за такт было возможно копирование только одного регистра, тогда как в Cannon Lake возможно копирование до трёх регистров за такт.

Ещё в новой микроархитектуре стали быстрее исполняться AES-инструкции. Это стало возможным за счёт того, что появились дополнительные AES-блоки, в результате чего темп исполнения вырос в 2,5–3 раза. Стоит заметить, что в Cannon Lake несколько увеличилась латентность инструкций, но при этом значительно возросла скорость их исполнения. То есть процессор немного дольше готовится к исполнению инструкции, зато выполняет её намного быстрее.

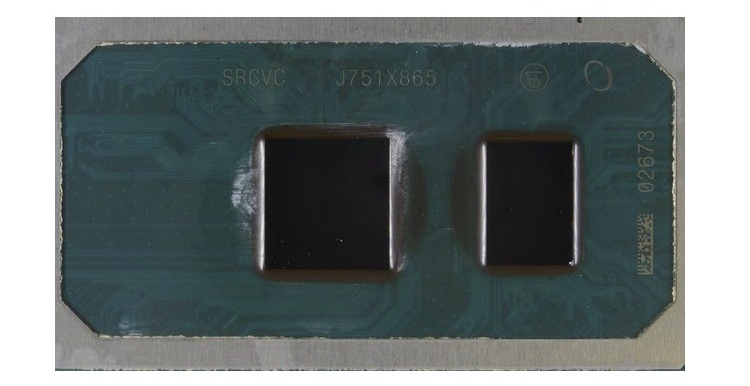

Core i3-8121U — первый и пока единственный серийный процессор на базе Cannon Lake

Также сообщается об уменьшении количества необходимых тактов для выполнения некоторых других инструкций. В целом же микроархитектура Cannon Lake предлагает ряд довольно интересных улучшений, которые положительно скажутся на скорости работы в некоторых приложениях и задачах. К сожалению, не все инструкции получили улучшения, так что увеличение скорости будет ощущаться не везде.

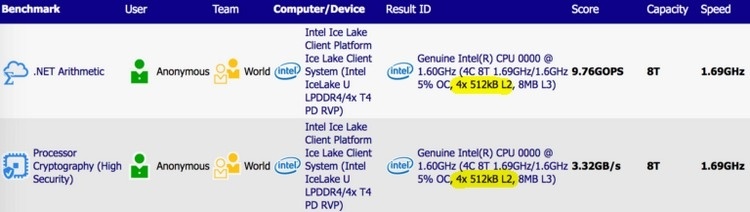

В конце добавим, что улучшения по части IPC ожидаются и в микроархитектуре Ice Lake, которая придёт на смену Cannon Lake. Получается, что если даже в нынешней архитектуре Cannon Lake наблюдается повышение IPC по сравнению со Skylake, то в будущей Ice Lake они могут быть несколько более значительными. Также отметим, что ещё летом появилась информация, что процессоры Ice lake предложат не только новое поколение встроенной графики, но и вдвое больший объём кеш-памяти второго уровня. Правда, ждать этих новинок придётся до конца следующего года, а может и вовсе до 2020 года.