Интерфейс ADM это внутренний стандарт компании «Инструментальные Системы». Он определяет правила соединения субмодулей ADM и базовых модулей. Ключевым элементом интерфейса является ПЛИС ADM. Изначально использовались ПЛИС серий FLEX10K и Acex 1K фирмы Altera. В 2003 году начался переход на ПЛИС Xilinx. Используются практически все серии ПЛИС от Spartan 2E до Kintex Ultrascale. Базовым элементом проекта ПЛИС является «тетрада». Данная статься именно об этом.

Базовый вариант интерфейса ADM на основе ПЛИС Altera получил название «Интерфейс ADM. Классическая реализация». Его особенностью является наличие в ПЛИС блока из шестнадцати регистров. Часть регистров обслуживала FIFO, часть регистров отводилась на обслуживание субмодуля. С ростом сложности изделий шестнадцати регистров стало недостаточно для организации управления. Ситуация осложняется тем, что на многих базовых модулях к ПЛИС подключены только пять или шесть адресных линий, на большее просто не хватает ножек. В такой ситуации логичным решением является организация косвенной адресации, но при этом требуется оставить быстрый доступ к регистрам FIFO. В результате появилась новая реализация, которая получила название «Интерфейс АDM. Прогрессивная реализация».

Логическая реализация

Основным элементом является тетрада. Тетрада это логический объект, который имеет четыре прямо адресуемых регистра и 1024 косвенно адресуемых регистры.

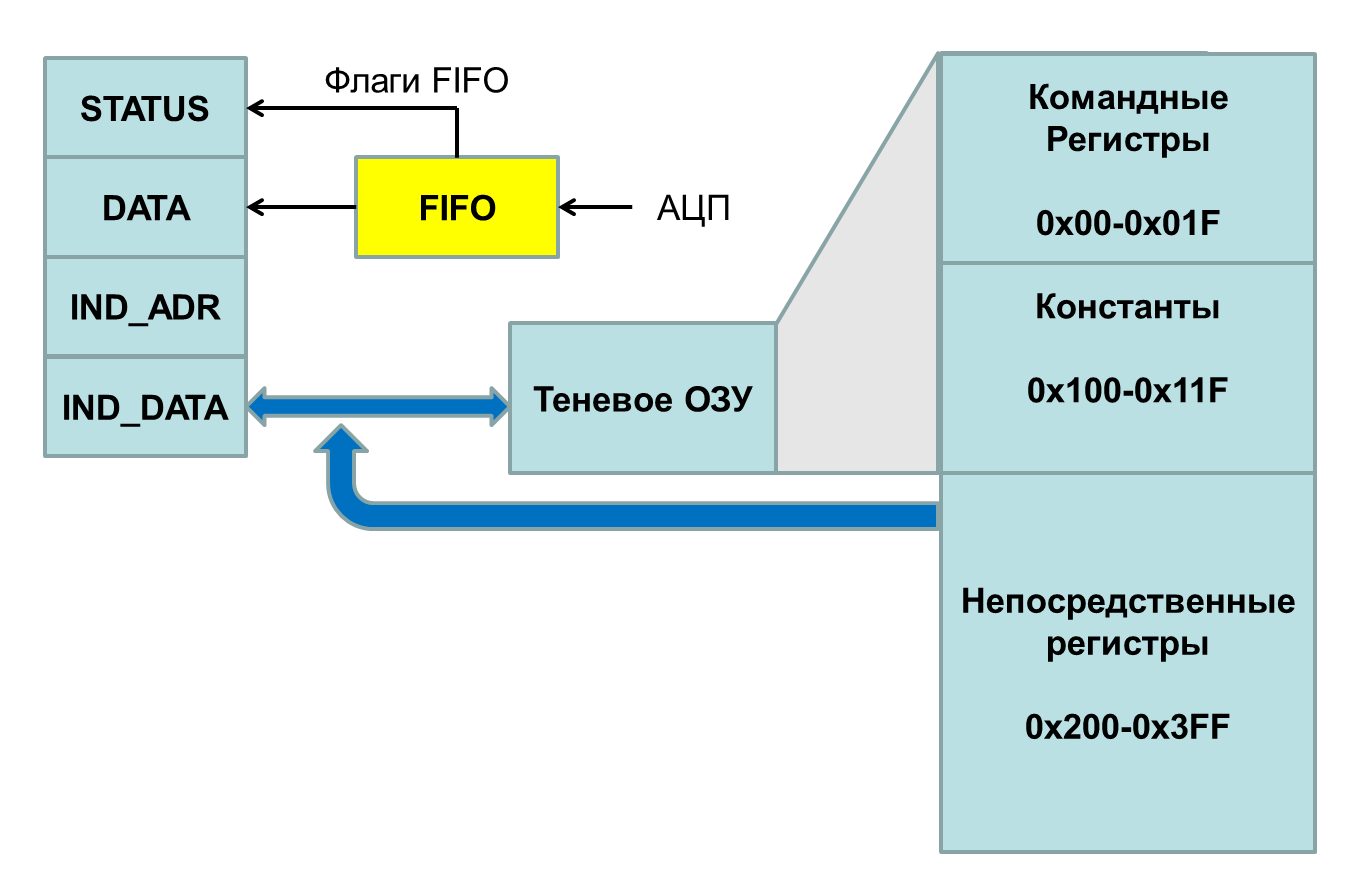

Логическая организация тетрады представлена на рисунке:

Прямые регистры:

- STATUS – регистр состояния FIFO, содержит флаги FIFO

- DATA – регистр данных FIFO

- IND_ADR – регистр косвенного адреса

- IND_DATA – регистр косвенных данных

Косвенно адресуемые регистры разделены на три группы.

- Группа 1 – командные регистры, адреса от 0x000 до 0x0FF

- Группа 2 – константы, адреса от 0x100 до 0x1FF

- Группа 3 – непосредственные регистры, адреса от 0x200 до 0x3FF

Главной особенностью командных регистров является то, что они могут изменить свое состояние либо в процессе сброса, либо в процессе записи в регистр. Это позволяет использовать для чтения из регистров теневое ОЗУ. А использование теневого ОЗУ позволяет резко сократить ресурсы ПЛИС для организации обратного чтения из регистров. Из-за теневого ОЗУ пришлось ввести определённую процедуру сброса тетрады, требуется сформировать сигнал сброса и прописать во все командные регистры значение 0.

Группа констант сохраняет наиболее важную информацию о тетраде. В первую очередь это идентификатор тетрады, номер версии а также наличие и направление работы FIFO. Идентификатор тетрады однозначно определяет набор регистров.

Непосредственные регистры позволяют реализовать регистры с любым поведением, в том числе дополнительные регистры состояния. При этом следует помнить, что реализация регистров на чтение потребует реализации мультиплексора, который является пожирателем ресурсов ПЛИС. Рекомендуется наибольшее число регистров помещать в группу командных и по минимуму – в группу непосредственных.

В настоящее время для организации теневого ОЗУ всех тетрад используется только один блок памяти ПЛИС. Это позволяет организовать в каждой тетраде 32 командных регистра и 32 константы. В любой момент это количество можно увеличить, но пока этого не потребовалось.

В прошивке ПЛИС может быть шестнадцать тетрад. Каждая тетрада управляет своей какой-либо законченной частью интерфейса.

Для примера приведён состав тетрад для прошивки модуля FMC107P и субмодуля FM216x250MDA

- TRD_MAIN — управление общими ресурсами

- BPI_FLASH — доступ к загрузочной FLASH

- TRD_DDS9956 — управление синтезатором

- PIOX_STD — управление цифровым портом

- TRD_FM216x250MDA_ADC — управление АЦП на субмодуле

- TRD_DDR3x — управление памятью DDR

- TRD_FM216x250MDA_DAC — управление ЦАП на субмодуле

Реализация на VHDL

Проект ПЛИС написан на языке VHDL. Для подключения тетрады используются специальные типы данных, что резко уменьшает объём текста. В настоящее время существует три типа подключения. В первую очередь они отличаются шириной шины данных, а во вторую – типом сигналов подключения.

Тип 1 – ширина шины данных 64 бита. Используются с сигнальными процессорами и интерфейсом PCI Express v1.1 x8

Тип 2 – ширина шины данных 128 бит. Используются с интерфейсом PCI Express v2.0 x8

Тип 3 – ширина шины данных 512 бит. Используется с интерфейсом PCI Express v3.0 x16

Во всех случаях тактовая частоты шины до 266 МГц. Если не требуется максимальное быстродействие, то рекомендуется снижать тактовую частоту для облегчения трассировки ПЛИС.

Базовым типом данных является тип bl_cmd

type bl_cmd is record

data_we : std_logic; -- 1 - запись в регистр DATA

cmd_data_we : std_logic; -- 1 - запись в регистр CMD_DATA

status_cs : std_logic; -- 0 - чтение из регистра STATUS

data_cs : std_logic; -- 0 - чтение из регистра DATA

cmd_data_cs : std_logic; -- 0 - чтение из регистра CMD_DATA

cmd_adr_we : std_logic; -- 1 - запись в регистр косвенного адреса

adr : std_logic_vector( 9 downto 0 ); -- косвенный адрес

data_oe : std_logic; -- 0 - разрешение выхода регистра DATA

end record;

Существует отдельный тип для описания сигнала запроса DMA

type bl_drq is record

en : std_logic; -- 1 - разрешение запроса DMA

req : std_logic; -- 1 - запрос на выполнение цикла DMA

ack : std_logic; -- 1 - выполнение цикла DMA

end record;

Описание тетрады типа 1 выглядит так:

component trd_user1 is

port (

-- GLOBAL

reset : in std_logic; -- 0 - сброс

clk : in std_logic; -- тактовая частота

cmd_data_in : in std_logic_vector( 15 downto 0 ); -- шина данных для CMD_DATA

cmd : in bl_cmd; -- команда для терады

data_out : out std_logic_vector( 63 downto 0 ); -- выход DATA

cmd_data_out : out std_logic_vector( 15 downto 0 ); -- выход регистров

bx_irq : out std_logic; -- 1 - прерывание от тетрады

bx_drq : out bl_drq; -- управление DMA

…. (остальные сигналы не показаны)

end component;

За исключением сигналов тактовой частоты и сброса используется шесть сигналов.

Для тетрады типа 2 число сигналов уменьшилось до двух.

component trd_user2 is

port (

-- GLOBAL

reset : in std_logic; -- 0 - сброс

clk : in std_logic; -- тактовая частота

host2trd : in type_host2trd; -- данные для тетрады

trd2host : out type_trd2host -- данные от тетрады

…. (остальные сигналы не показаны)

end component;

type type_trd2host is record

status : std_logic_vector( 15 downto 0 ); --! регистр STATUS

cmd_data : std_logic_vector( 15 downto 0 ); --! данные регистров

data : std_logic_vector( 127 downto 0 ); --! данные регистра DATA

drq : bl_drq; --! запрос DMA

irq : std_logic; --! запрос прерывания

fifo_rstp : std_logic; --! 1 - сброс FIFO

end record;

type type_host2trd is record

cmd : bl_cmd; --! команда для тетрады

cmd_data : std_logic_vector( 15 downto 0 ); -- шина для записи в регистры

data : std_logic_vector( 127 downto 0 ); -- шина 128 разрядов для записи в регистр DATA

end record;

С ростом объёма ПЛИС увеличиваются трудности при размещении компонентов тетрад внутри ПЛИС. Это связано с высокой тактовой частотой и большой длиной соединений.

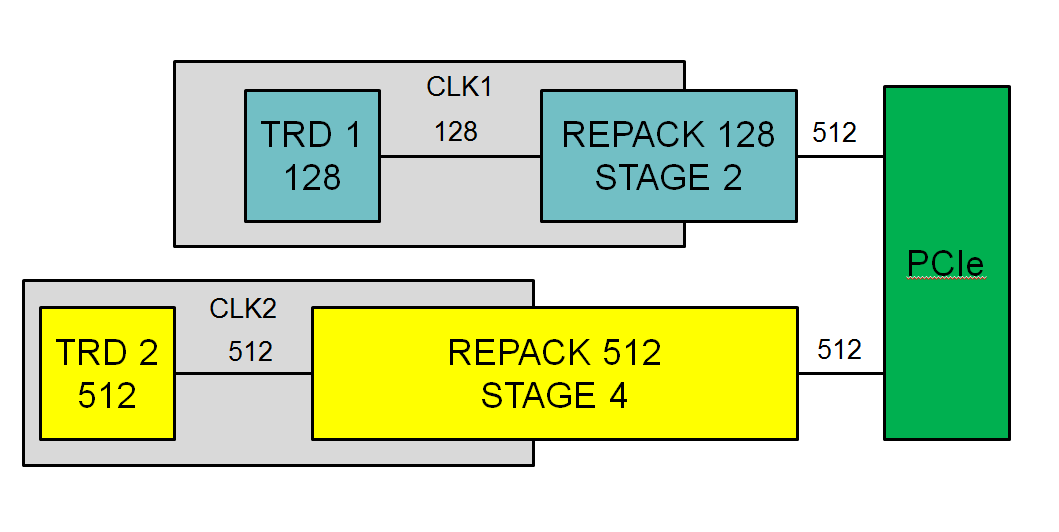

При этом высокая тактовая частота нужна только для передачи данных. Для обращения к регистрам достаточно 100 МГц. Типы подключения 1 и 2 используют только один сигнал тактовой частоты. Для типа 3 используется две тактовые частоты и дополнительный компонент repack. Компонент repack установлен между тетрадой и узлом подключения к шине. Он имеет параметр STAGE, который определяет количество дополнительных триггеров в шине данных. Кроме того, возможна реализация нескольких модификаций для подключения тетрад типа 1 и 2. На рисунке представлена конфигурация в которой через компонент REPACK_128 подключена тетрада типа 2 и через компонент REPACK_512 подключена тетрада типа 3, при этом используется параметр STAGE=4 который позволяет установить тетраду в любом месте ПЛИС Virtex 7.

В заключение хотелось бы отметить что тетрады оказались очень удобными для модульного построения прошивок ПЛИС и модульного построения программного обеспечения. Концепция тетрад активно используется более 12 лет. Тетрады пережили рост ПЛИС и изменение серий от Spartan 2E до Virtex 7 и внедряются в серию Ultrascale. Скорость ввода поднялась от 200 Мбайт/с до 11 Гбайт/с. Поддержано большое количество субмодулей. Произошёл переход от внутрифирменного стандарта ADM к международному стандарту FMC.

Более подробное описание тетрад приведено в документе: «DCR0340 – Интерфейс ADM. Прогрессивная реализация». В соответствии с правилами Habrahabr, ссылку на документ дать не могу.

Автор: dsmv2014