Всем привет! Меня зовут Максим, я работаю инженером в одной компании. Фирма делает серверы и другое железо на POWER-архитектуре (какое и почему именно такое — позже расскажут другие), а я пока хочу показать участок системной платы сервера — это моя зона ответственности.

Вообще здесь будет нечто вроде рабочего журнала (worklog-а)— вместе с коллегами будем постить рассказы о зарождении жизни в железках. Сначала про сервер, а дальше и про остальное.

Как сюда лучше всего поставить преобразователи напряжения?

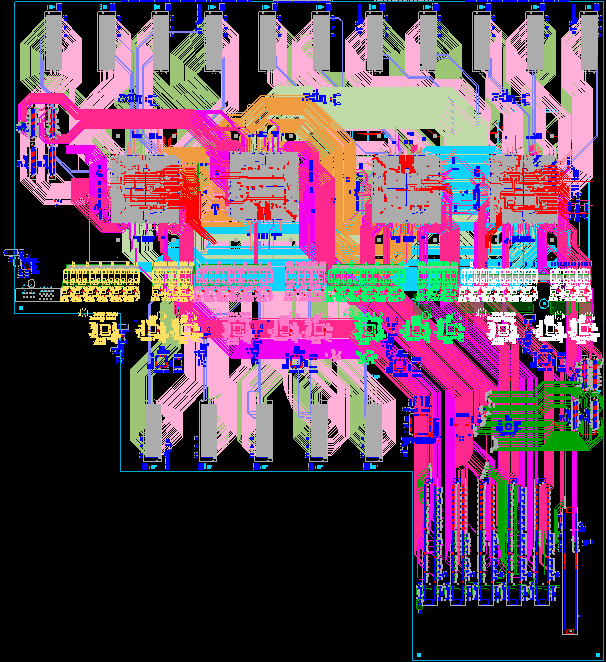

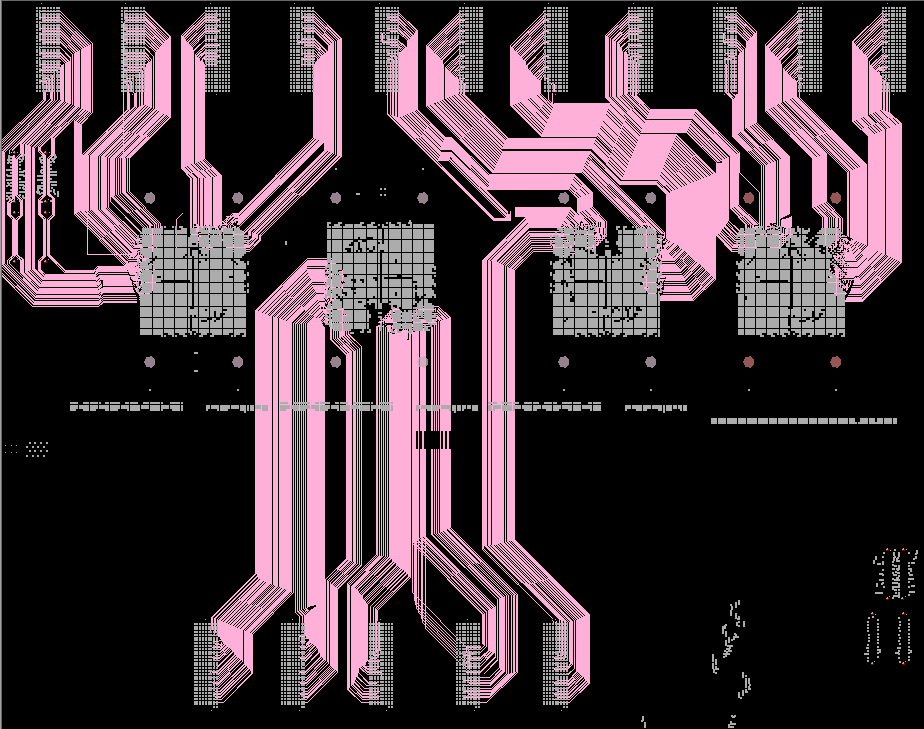

На скрине выше — не результат галлюцинаций художника, творящего в стиле ПОП-АРТ, а системная плата, на которой надо уместить четыре группы преобразователей напряжения — по одной на каждый процессор (жёлтые, розовые, ярко-зелёные и белые на скриншоте).

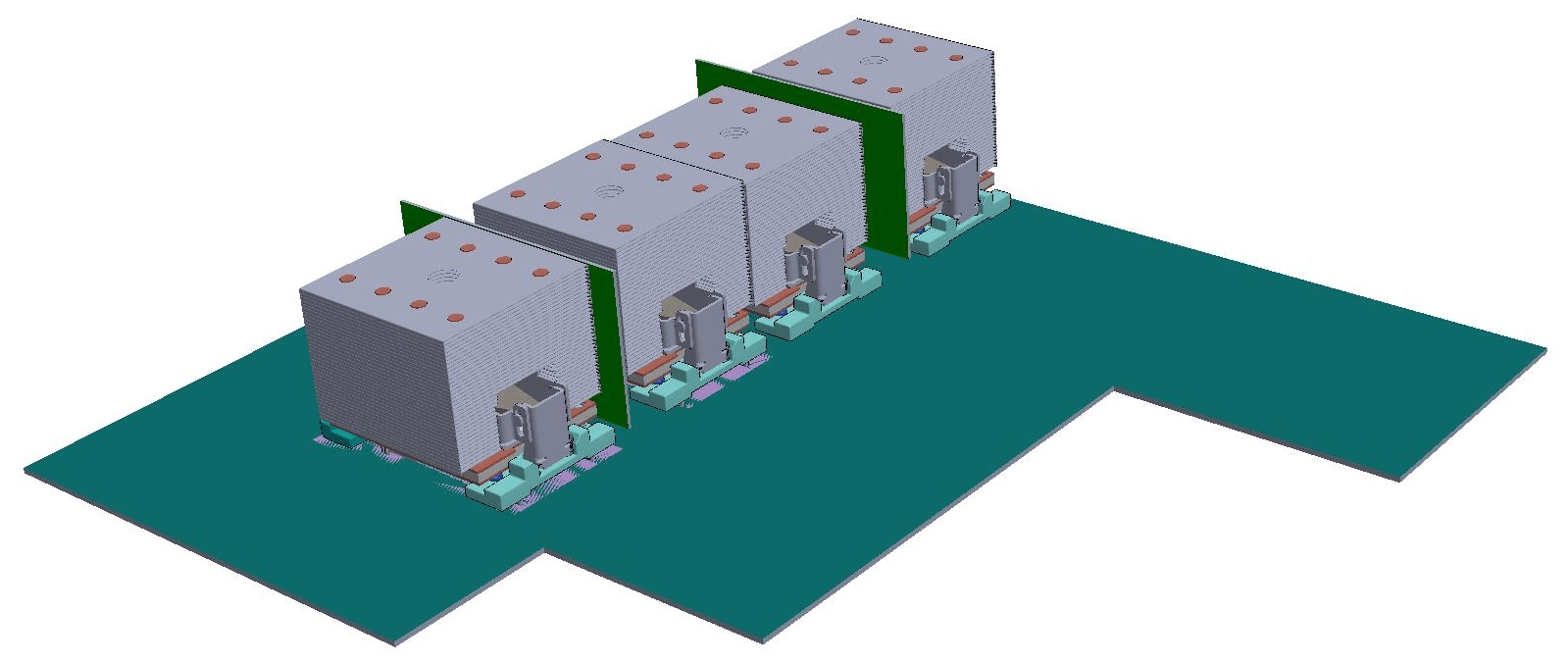

Сначала хотели вынести их на внешние платы, как на рисунке ниже:

Первоначальная идея по размещению преобразователей

По изначальной задумке, каждая плата должна была нести VRM-ы для двух процессоров и связанных с ним модулей памяти. Но после проработки решили отказаться от этого варианта — дико большой ток требует большого CardEdge-разъёма, что сильно усложнит трассировку межпроцессорных шин.

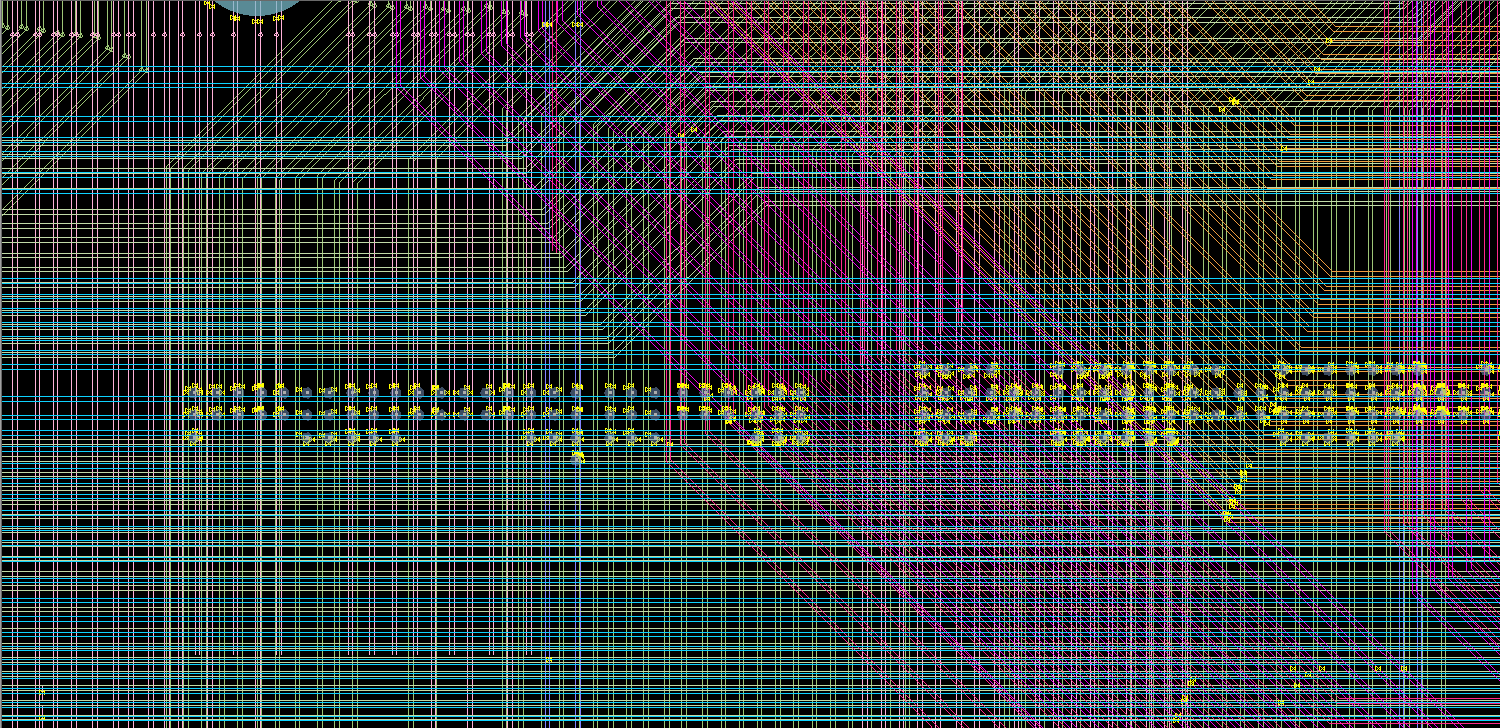

Теперь пробуем запилить VRM-ы на системной плате. Это тоже усложняет трассировку — теперь уже высокоскоростных шин, т.к. придётся менять расположение дорожек, чтобы огибать переходные отверстия (vias), которые необходимы для подведения напряжений на процессоры от преобразователей. А отверстий нужно не мало! Для процессоров и модулей памяти необходим большой ток, и нужно плотность этого самого тока, проходящего через переходные отверстия, минимизировать. Если сэкономить на количестве переходных отверстий, то это вызовет их перегрев (из-за большой плотности тока) и со временем деградацию до полного выгорания.

Практически скриншот из TRON 2.0, хочется плакать кровавыми слезами. Отверстия подсвечены жёлтым — на самом деле это подсветка ошибок из-за пересечения с ними дорожек различных шин. Нужно все эти дорожки отводить в сторону.

Вообще, сложность проекта в рамках моих задач состоит в том, что приходится трассировать на плате, помимо шин питания с большим током (до 250 А!), много высокоскоростных шин — PCIe Gen3 (8 Gbps), DMI (9.6 Gbps, Differential Memory Interface, шина подключения чипов буфера памяти Centaur), межпроцессорные шины A-bus (6.4 Gbps, SMP линк).

Если интересно, можно отдельно про них написать.

Компонентов тоже немало — 4 процессора, 16 разъёмов для райзер-карт памяти DDR4, в общей сложности 14 разъёмов для PCIe (из которых 8 — NanoPitch, а 6 — обычные разъёмы для карт расширения), и монтаж выходит очень плотный. Первый скрин даёт достаточное представление о масштабе бед — это упрощённое изображение с изрядным количеством скрытых от показа компонентов, чтобы и без того плотную картинку не перегружать.

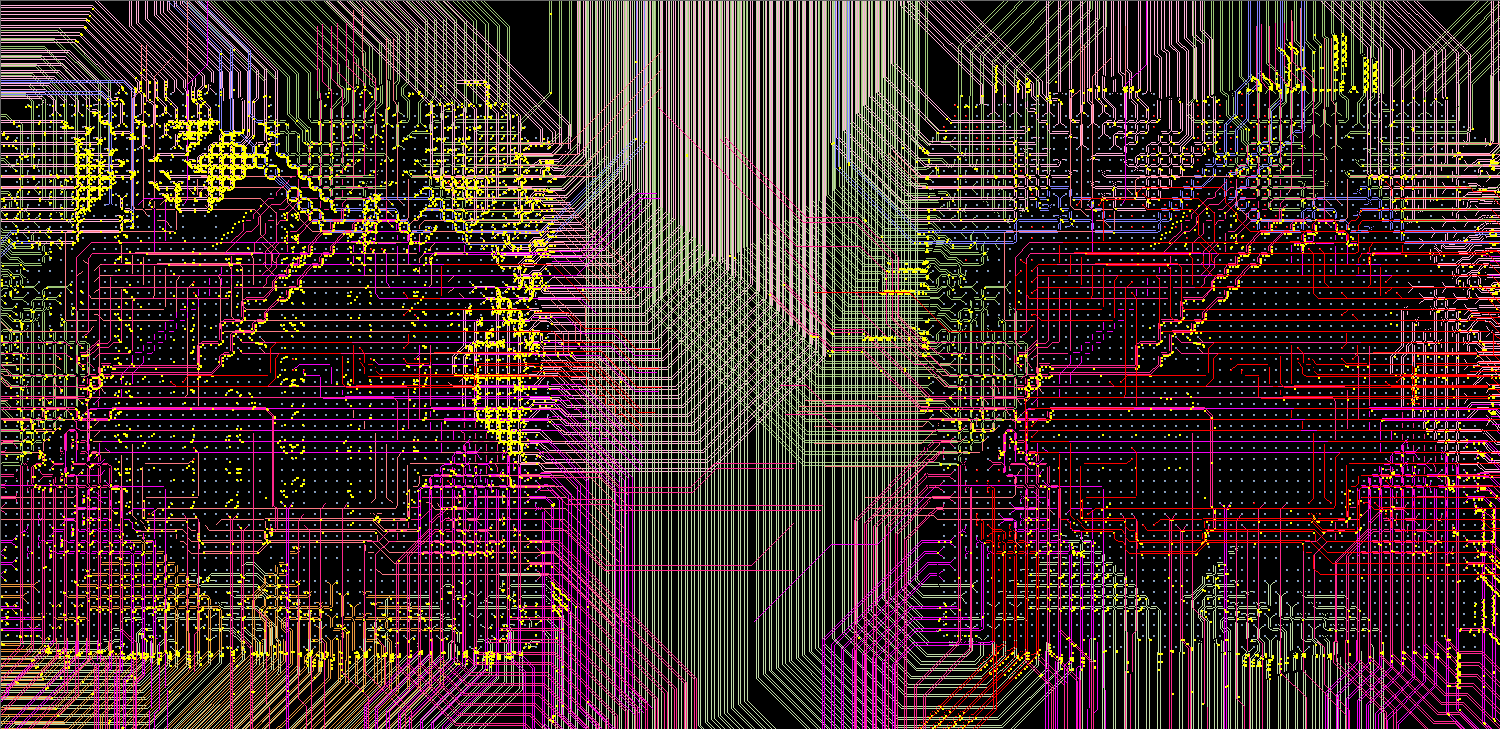

Участок между двумя процессорами. Удалось проложить дорожки между ними весьма плотно.

Много высокоскоростных интерфейсов — много ограничений. Приходится строго соблюдать требования по трассировке — максимальная длина, статическая и динамические фазы в дифференциальных парах; дистанция между дифф-парами; максимальный разброс по длине в группе, волновое сопротивление и т.д.

Это, в свою очередь, накладывает ограничения на маршруты шин по плате, выбору материала печатной платы (материал с низкими потерями), количеству слоёв, и т.д.

Сейчас у нас стэк с 28 слоями — из них 4 слоя выделено под шины питания, для увеличения площади полигонов питания — это позволяет минимизировать IR drop (падение напряжения на проводнике). Хотим не превышать это число слоёв, и думаю, должны это сделать.

В общем, такие вот рабочие будни. Привыкаешь смотреть на такие схемы пристальным взглядом — а потом замечаешь, что они в своём роде даже художественны, как смешение линий и цветовых пятен различных форм и оттенков. Да и сама трассировка таких масштабов — само по себе искусство.

Напоследок хочу показать ещё один скрин, который скрывает целую историю:

Это не пришествие Ктулху из морской пучины.

Из-за особенностей расположения разъёмов памяти пришлось развернуть один процессор на 180 градусов. Почему нельзя было расположить разъёмы памяти иначе? Это уже история следующей серии и героем в ней буду не я.

Автор: YADRO